# **Single-Electron Devices and Their Applications**

Konstantin K. Likharev Department of Physics, State University of New York at Stony Brook Stony Brook, NY 11794-3800 klikharev@ccmail.sunysb.edu

#### Abstract

The goal of this paper is to review in brief the basic physics of single-electron devices, as well as their current and prospective applications. These devices, based on the controllable transfer of single electrons between small conducting "islands", have already enabled several important scientific experiments. Several other applications of analog single-electron devices in unique scientific instrumentation and metrology seem quite feasible. On the other hand, the prospect of silicon transistors being replaced by single-electron devices in integrated digital circuits faces tough challenges and remains uncertain. Nevertheless, even if this replacement does not happen, single-electronics will continue to play an important role by shedding light on the fundamental size limitations of new electronic devices. Moreover, recent research in this field has generated some exciting by-product ideas which may revolutionize random-access-memory and digital-data-storage technologies.

**Keywords** - Single-electron tunneling, Fowler-Nordheim tunneling, single-electron devices, Coulomb blockade, supersensitive electrometry, single-electron spectroscopy, dc current standards, temperature standards, random access memories, floating-gate memories, logic circuits, data storage.

# I. INTRODUCTION: BASIC PHYSICS AND SCALING

The manipulation of single electrons was demonstrated in the seminal experiments by Millikan at the very beginning of the century, but in solid state circuits it was not implemented until the late 1980s, despite some important earlier background work [1-5]. The main reason for this delay is that the manipulation requires the reproducible fabrication of very small conducting particles, and their accurate positioning against external electrodes. The necessary nanofabrication techniques have become available during the past two decades, and have made possible a new field of solid state physics, *single-electronics* (see Refs. 6-8 for its general reviews).

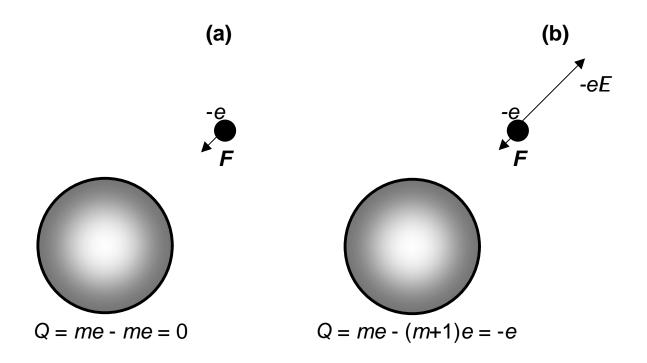

Figure 1 illustrates the basic concept of single-electronics. Let a small conductor (traditionally called an *island*) be initially electroneutral, i.e. have exactly as many (*m*) electrons as it has protons in its crystal lattice. In this state the island does not generate any appreciable electric field beyond its borders, and a weak external force *F* may bring in an additional electron from outside. (In most single-electron devices, this injection is carried out by tunneling through an energy barrier created by a thin insulating layer). Now the net charge *Q* of the island is (*-e*), and the resulting electric field *E* repulses the following electrons which might be added. Though the fundamental charge  $e \approx 1.6 \times 10^{-19}$  Coulomb is very small on the human scale of things, the field *E* is inversely proportional to the square of the island size, and may become rather strong for nanoscale

structures. For example, the field is as large as  $\sim$ 140 kV/cm on the surface of a 10-nm sphere in vacuum.

The theory of single-electron phenomena (see the next section) shows that a more adequate measure of the strength of these effects is not the electric field, but the *charging energy*

$$E_c = e^2/C,\tag{1}$$

where *C* is the capacitance of the island<sup>1</sup>. When the island size becomes comparable with the de Broglie wavelength of the electrons inside the island, their energy quantization becomes substantial (see, e.g., reviews [10-13]). In this case the energy scale of the charging effects is given by a more general notion, the *electron addition energy*  $E_a$ . In most cases of interest,  $E_a$  may be well approximated by the following simple formula:

$$E_a = E_c + E_k. \tag{2}$$

Here  $E_k$  is the quantum kinetic energy of the added electron; for a degenerate electron gas  $E_k = 1/g(\varepsilon_F)V$ , where V is the island volume and  $g(\varepsilon_F)$  is the density of states on the Fermi surface.

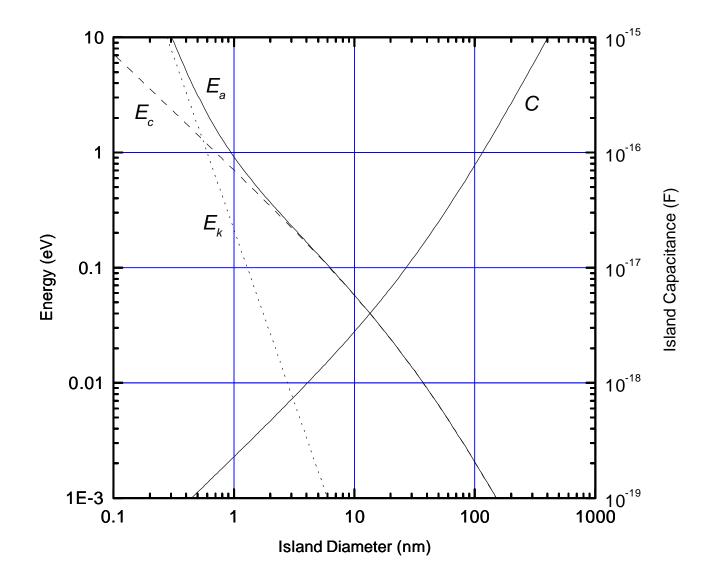

Figure 2 shows the total electron addition energy as a function of the island diameter, as calculated using Eq. (2) for a simple but representative model. For 100-nm-scale devices which were typical for the initial stages of experimental single-electronics,  $E_a$  is dominated by the charging energy  $E_c$  and is of the order of 1 meV, i.e. ~ 10 K in temperature units. Since thermal fluctuations suppress most single-electron effects unless

$$E_a \ge 10 \ k_B T,\tag{3}$$

these experiments have to be carried out in the sub-1-K range (typically, using helium dilution refrigerators).

On the other hand, if the island size is reduced below ~10 nm,  $E_a$  approaches 100 meV, and some single-electron effects become visible at room temperature. However, most suggested digital single-electron devices require even higher values of  $E_a$  (~ 100  $k_BT$ ) in order to avoid thermally-induced random tunneling events, so that for room temperature operation the electron addition energy  $E_a$  has to be as large as a few electron-volts, and the minimum feature size of single-electron devices has to be smaller than ~1 nm (Fig. 2). In this size range the electron quantization energy  $E_k$  becomes comparable with or larger than the charging energy  $E_c$  for most materials; this is why islands this small are frequently called *quantum dots*. Their use involves not only extremely difficult nanofabrication technology (especially challenging for large scale integration), but also some major physics problems including the high sensitivity of transport properties to small variations of the quantum dot size and shape. This is why it is very important to develop single-electron devices may work in the size range where  $E_c > E_k$  even at room temperature, thus avoiding complications stemming from the energy quantization effects.

<sup>&</sup>lt;sup>1</sup> For a *two-electrode* capacitor, the elementary charging energy is of course  $e^2/2C = E_c/2$ , rather than  $E_c$ . However, if a *single* small conductor is charged with electrons from a source kept at a fixed electrochemical potential  $\mu$ , this is  $E_c$  which gives the electrostatic contribution to the energy necessary for the transfer of one additional electron to the conductor:  $e\Delta\mu \equiv E_a \approx E_c + \text{kinetic energy} - \text{see Eq. (2)}$ .

The objective of this paper is to give a brief review of the present status of applied singleelectronics. I will start with an introduction of the theory of single-electron tunneling (Sec. II). It will allow us to discuss (in Sec. III) the most important single-electron phenomena, devices and circuit components. Analog applications of the devices will be described in Sec. IV, while the prospects of digital applications will be discussed in Sec. V. In the concluding Sec. VI, I will try to summarize my vision of the prospects and problems faced by the field.

Due to the paper length restrictions I will not be able to mention many important contributions to the rapidly growing pool of literature on single-electronics; I am expressing my apology to the authors and hope for their understanding.

#### **II. THEORETICAL BACKGROUND**

#### A. Orthodox Theory

Throughout the history of single-electronics, a unique guiding role has been played by a simple but very effective "*orthodox*" theory which was pioneered (for a particular case) by Kulik and Shekhter [5] and later generalized to other systems - see, e.g., Ref. 7 or Ref. 13 for a detailed review. The theory makes the following major assumptions:

• The electron energy quantization inside the conductors is ignored, i.e. the electron energy spectrum is treated as continuous. Strictly speaking this assumption is valid only if  $E_k \ll k_B T$ , but it frequently gives an adequate description of observations as soon as  $E_k \ll E_c$  (cf. Fig. 2).

• The time  $\tau_t$  of electron tunneling through the barrier is assumed to be negligibly small in comparison with other time scales (including the interval between neighboring tunneling events). This assumption is valid for tunnel barriers used in single-electron devices of practical interest, where  $\tau_t \sim 10^{-15}$  s.

• Coherent quantum processes consisting of several simultaneous tunneling events ("*cotunneling*") are ignored. This assumption is valid if the resistance R of all the tunnel barriers of the system is much higher than the quantum unit of resistance  $R_o$ :

$R \gg R_{\varrho}, \qquad R_{\varrho} = h/4e^2 \approx 6.5 \text{ k}\Omega.$  (4)

The latter relation is of principal importance for single-electronics as a whole.<sup>2</sup>

Despite the limitations listed above, the orthodox theory is in *quantitative* agreement with virtually all the experimental data for systems with metallic conductors (with their small values of the electron wavelength on the Fermi surface,  $\lambda_F$ ) and gives at least a qualitative description of most results for most semiconductor structures (where the quantization effects are more noticeable, due to larger  $\lambda_F$ ).

<sup>&</sup>lt;sup>2</sup> This field really took off when it was recognized [14, 15] that Eq. (4) ensures the localization of each electron within a particular conducting island of the system at any particular instant. This fact shows that tunnel barriers with low transparency may effectively suppress the quantum-mechanical uncertainty of the electron location. Notice that only this suppression makes controllable single-electron manipulation possible. (In this sense single-electronics *does not* fall into the much advertised category of "quantum electronic devices". Of course, single-electron devices *do* use quantum properties of matter, but so do semiconductor transistors.)

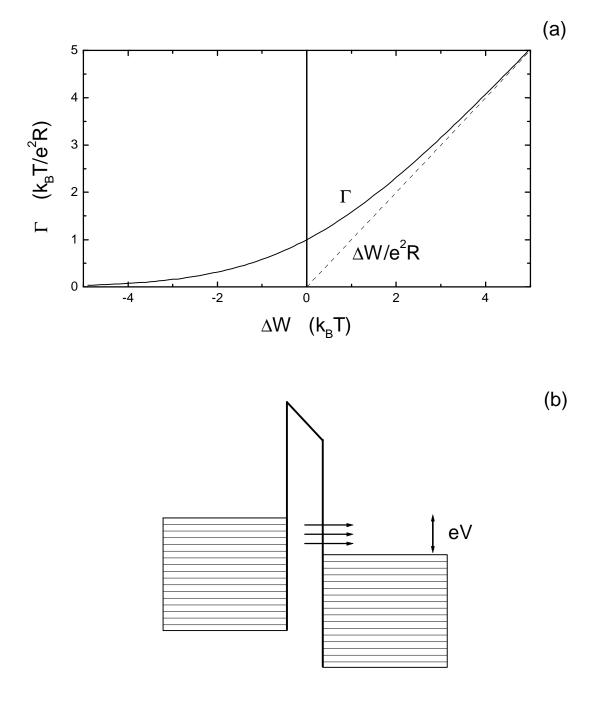

The main result of the theory can be formulated as follows: the tunneling of a single electron through a particular tunnel barrier is always a *random event*, with a certain rate  $\Gamma$  (i.e. probability per unit time) which depends solely on the reduction  $\Delta W$  of the free (electrostatic) energy of the system as a result of this tunneling event. Within the orthodox theory this dependence may be expressed with a universal formula

$$\Gamma(\Delta W) = (1/e) I(\Delta W/e) [1 - \exp\{-\Delta W/k_B T\}]^{-1},$$

(5)

where I(V) is the "seed" dc *I*-*V* curve of the tunnel barrier in the absence of single-electron charging effects. (In many cases, the Ohmic approximation I(V) = V/R is quite acceptable.)  $\Delta W$  may be readily found from the system's electrostatics; a few simple examples will be considered below. Frequently the following general expressions are rather useful:

$$\Delta W = e(V_i + V_f)/2, \tag{6a}$$

$$\Delta W = e(V_i - V_t), V_t \equiv e(C^1)_{kl} - e[(C^1)_{kk} + (C^1)_{ll}]/2,$$

(6b)

where  $V_i$  and  $V_f$  are voltage drops across the barrier before and after the tunneling event, respectively, while  $C^{-1}$  is the reciprocal capacitance matrix of the system, and k and l are the numbers of the islands separated by this particular barrier.

Figure 3a shows the dependence given by Eq. (5); at low temperatures ( $k_BT \ll \Delta W$ ) only tunneling events decreasing the electrostatic energy (and dissipating the difference) are possible, and their rate is proportional to  $\Delta W$ . The latter fact is easy to comprehend: an increase in applied voltage increases the number of electron states in the source electrode which may provide an electron capable of tunneling into an empty state of the drain electrode.

Though Eqs. (5) and (6) are rather simple, the calculation of properties of even some basic single-electron systems runs into a technical problem: in many situations, several tunneling events are possible at the same time, and the orthodox theory only gives the chances of a particular outcome. Hence, some sort of statistical calculation scheme becomes inevitable. For systems with relatively few islands, i.e. with a limited set of possible charge states  $\{i\}$ , Eq. (5) may be plugged into the system of "master" equations [5, 14, 15]:

$$dp_i/dt = \sum_j \left( \Gamma_{j \otimes i} p_j - \Gamma_{i \otimes j} p_i \right)$$

(7)

describing the time evolution of probability  $p_i$  of each state. After this system has been solved, the probabilities  $p_i$  may be used for a straightforward calculation of average values and fluctuations of any variable. A nice example of the implementation of this approach is the series of computer programs SETTRANS for the fast calculation of dc *I-V* curves and white noise of single-electron transistors, created by A. Korotkov.<sup>3</sup>

For more complex systems the multi-dimensional space of all possible charge states may become too large, and the only practical method is to simulate the random dynamics of the system by a Monte Carlo method [16]. In this procedure, Eq. (5) is used to establish the correct statistics of the randomly generated events. After a sufficient number of implementations have been

<sup>&</sup>lt;sup>3</sup> MS-DOS versions of these programs are available via anonymous ftp from the site hana.physics.sunysb.edu/pub/settrans/dos.

accumulated, variables of interest may be evaluated by averaging over this ensemble. Several programs of this type have been developed by various research groups. Of those publicly available, SIMON developed by C. Wasshuber and his collaborators at the Technical University of Vienna, Austria [17] features a graphical user interface and also allows an approximate account of cotunneling.<sup>4</sup> On the other hand, MOSES developed by R. Chen and collaborators at Stony Brook<sup>5</sup> only has a text interface and is limited to the orthodox theory, but allows a broader range of circuit elements and analyses. The currently available version 1.1 of MOSES is also considerably faster than the available version 1.3 of SIMON [18]. In certain cases, a combination of both numerical methods may be useful [19].

### B. Effects Beyond the Orthodox Theory

Experiments with single-electron devices have indicated several features which are not accounted for by the orthodox theory. In non-superconducting systems, the most important effects are:

1). *Cotunneling*. This effect was first predicted in 1989 [20] and observed experimentally soon after [21] (for a review, see Ref. 50). The essence of the effect is that the tunneling of several (N>1) electrons through different barriers at the same time is possible as a single coherent quantum-mechanical process. The rate of this process is crudely ( $R_Q/R$ )<sup>N-1</sup> times less than that for the single-electron tunneling described by Eq. (5) of the orthodox theory. If the condition expressed by Eq. (4) is satisfied, this ratio is rather small; cotunneling can nevertheless be clearly observed within the Coulomb blockade range where orthodox tunneling is suppressed - see Sec. III below.

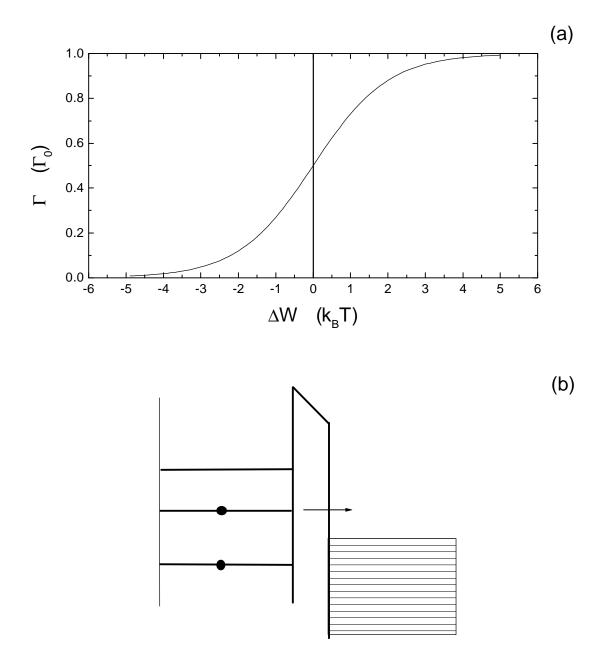

2). Discrete Energy Levels. For very small islands, the quantum splitting  $E_k$  between electron energy levels may become larger than  $E_c$  and  $k_BT$  (see Fig. 2 and its discussion in Sec. I). The generalization of the orthodox theory to this case has been carried out by Averin and Korotkov [23] who considered a situation where tunneling is only possible between islands with discrete levels and larger electrodes where electrons still have a continuous spectrum. They have shown that if the tunneling barriers are not extremely thin, i.e. their seed tunneling rate  $\Gamma_0$  is not too large ( $\hbar\Gamma_0 < k_BT$ ), the situation may again be described with master equations similar to Eq. (7) of the orthodox theory, but with a different energy dependence of the tunneling rate to/from a certain quantum level:

$$\Gamma \left( \Delta W \right) = \Gamma_0 \left[ 1 + \exp\{-\Delta W / k_B T\} \right]^{-1}.$$

(8)

This dependence (Fig. 4a) repeats (and results from) the Fermi distribution of electrons in the bulk electrode. (In fact, the orthodox rate (5) may be obtained as a sum of the rates (8) over all the levels of a continuous spectrum of the island). Another difference is that the summation in the master equations should be extended over two indices: one for the total number of electrons (as in Eq. (7)), and another for the electron distribution between the energy levels, at a fixed number of electrons. This makes the solution to master equations more complex.

<sup>&</sup>lt;sup>4</sup> Information on the distribution of SIMON can be found on the Web site http://members.magnet.at/catsmeow/.

<sup>&</sup>lt;sup>5</sup> MOSES 1.1 is available in both MS-DOS and UNIX versions via anonymous ftp from the site hana.physics.sunysb.edu/pub/moses.

If the system has more than one quantum dot, tunneling between them may become important. If the energy loss effects are not too significant, this tunneling leads only to coherent hybridization of the quantum dot levels, similar to that well studied in atomic and molecular physics. Inelastic tunneling from an island to bulk electrodes, described by Eq. (8), may bring a substantial dissipation into this system and suppress the system coherence - see, e.g., experiments [24-26] with "artificial molecules", and review [12].

In general, energy quantization effects have not yet led to suggestions for any new practical applications, with the exception of single-electron spectroscopy (Sec. IV.B) which is still limited to fundamental physics studies, and some highly controversial logic device proposals (Sec. V.B). This is why a review of single-electron devices can be based mostly on the predictions of the orthodox theory.

# **III. BASIC SINGLE-ELECTRON DEVICES**

Let us start with a discussion of cases in which single-electron charging effects do *not* appear. First, consider a tunnel junction with a *fixed voltage V* across it ( $V_i = V_j = V$ ). Here, for two possible directions of electron tunneling, Eq. (6) yields  $\Delta W = \pm eV$ , and according to Eq. (5) the net current is  $I = e \times [\Gamma(eV) - \Gamma(-eV)] = I(V)$ , i.e. we have come back to the seed dc *I-V* curve. This is natural, since in this system a single-electron tunneling event does not change *V*, i.e. the single-electron charge quantization does *not* lead to any noticeable effects, <sup>6</sup> even if the junction size is very small. A possible way to describe the same fact is to say that the large stray capacitance of the external electrodes leading to the junction adds up to the junction capacitance (however small), so that the total capacitance *C* does not satisfy the condition (3).<sup>7</sup>

Even more importantly, the orthodox theory predicts that the effects of single-electron discreteness may be ignored in *any* solid state device which does not have small conducting islands separated from the external electrodes by sufficiently high tunnel barriers. (The quantitative criterion of the notion "high barrier" is provided by Eq. (4)). The most important practical example may be a small-size MOSFET which does not exhibit any immediate single-electron effects even if the average number of carriers in its channel is smaller than one, since in these devices the channel-contact resistance is typically much lower than  $R_Q$ . The physical interpretation of this fact is that in systems without sufficiently high tunnel barriers the electron wavefunctions are well extended, and electrons cannot be treated as classical, localized particles.

Now let us turn to situations in which the single-electron charging effects do appear.

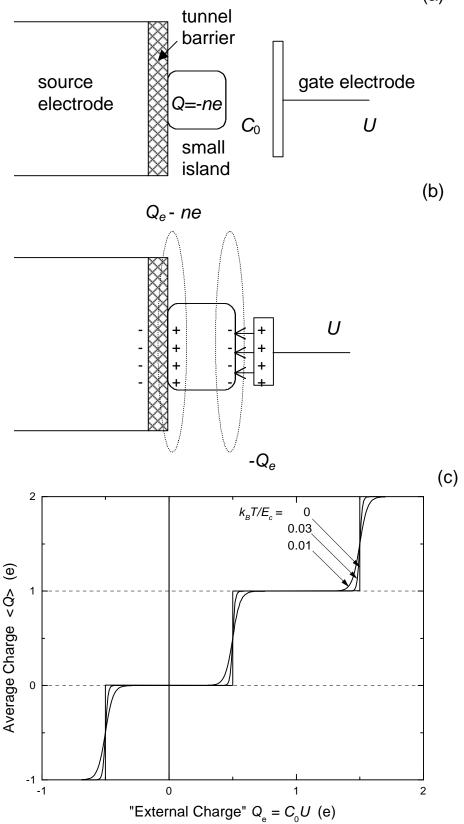

# A. Single-Electron Box

Figure 5a shows the conceptually simplest device, the "*single-electron box*".<sup>8</sup> The device consists of just one small island separated from a larger electrode ("*electron source*") by a tunnel

<sup>&</sup>lt;sup>6</sup> Besides shot noise which appears at  $eV/2 > k_BT$ .

<sup>&</sup>lt;sup>7</sup> More detailed analysis [14, 15] shows that even if the stray capacitance is carefully eliminated, the singleelectron charging effects would not show up, because the lead impedance  $Z(\omega)$  is typically much less than the quantum unit of resistance (4), and as a result, quantum fluctuations of the environment smear out the charging effects. A quantitative theory of this smearing has been developed by Nazarov [27]. (A simpler derivation of the same result was given by Devoret *et al.* [28]; see also the review [13].)

barrier. An external electric field may be applied to the island using another electrode ("*gate*") separated from the island by a thicker insulator which does not allow noticeable tunneling. The field changes the electrochemical potential of the island and thus determines the conditions of electron tunneling. Elementary electrostatics shows that the free (Gibbs) energy of the system may be presented as

$$W = Q^2/2C_{\Sigma} + (C_0/C_{\Sigma})QU + \text{const}, \qquad (9)$$

where Q = -ne is the island charge (*n* is the number of uncompensated electrons),  $C_0$  is the islandgate capacitance, while  $C_{\Sigma}$  is the total capacitance of the island (including  $C_0$ ). Usually, this expression is re-written as

$$W = (ne - Q_e)^2 / 2C_{\Sigma} + \text{const}, \qquad (10)$$

where parameter  $Q_e$ , which is defined as

$$Q_e \equiv UC_0, \tag{11}$$

is usually called the "*external charge*". The physical sense of this definition only becomes apparent for the case when the electric field between the gate and island is well localized (Fig. 5b); then (- $Q_e$ ) is just the polarization charge of the island which is bound by the gate field and is thus taken out of the energy balance of the tunnel junction.

From the definition (9) it is evident that in contrast with the discrete total charge of the island, the variable  $Q_e$  is *continuous*, and may be a fraction of the elementary charge e. At low temperatures Eq. (5) shows that the single-electron tunneling merely minimizes W; an elementary calculation using Eq. (10) shows that Q is a step-like function of  $Q_e$ , i.e. of the gate voltage (Fig. 5c), with a fixed distance between the neighboring steps:

$$\Delta Q_e = e, \qquad \Delta U = e/C_0 = \text{const.} \tag{12}$$

If the temperature is increased to  $k_BT \sim E_c$ , this "*Coulomb staircase*" is gradually smeared out by thermal fluctuations.

The physics of the Coulomb staircase is very simple: increasing gate voltage U attracts more and more electrons to the island. The discreteness of electron transfer through low-transparency barriers necessarily makes this increase step-like. This is all very natural and apparently trivial. What *is* surprising is that even such a simple device allows a reliable addition/subtraction of single electrons to/from an island with an enormous (and unknown) number of background electrons, of the order of 1 million in typical low-temperature experiments with 100-nm-scale aluminum islands. This is of course simply a consequence of the enormous strength of the unscreened Coulomb interaction, which has already been discussed in Sec. I.

Notice, however, two major drawbacks of the single-electron box as an electronic circuit component. First, it does not have internal memory: the number n of the electrons in the box is a unique function of the applied voltage U, so that this structure cannot be used for information

<sup>&</sup>lt;sup>8</sup> The basic properties of this system were well understood by Lambe and Jaklevic [4] in the context of their experiments with granular tunnel structures, while its quantitative theory was given by Kulik and Shekhter [5]. Experimentally, however, the properties of a single device were not measured until 1991 [29].

storage. The second problem is that the box cannot carry dc current, so that an ultrasensitive electrometer is necessary to measure its charge state - see, e.g., Ref. 29.

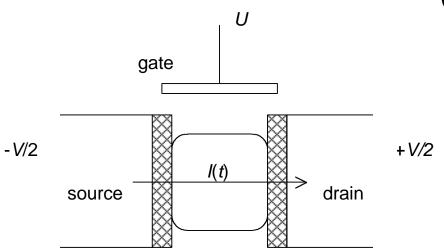

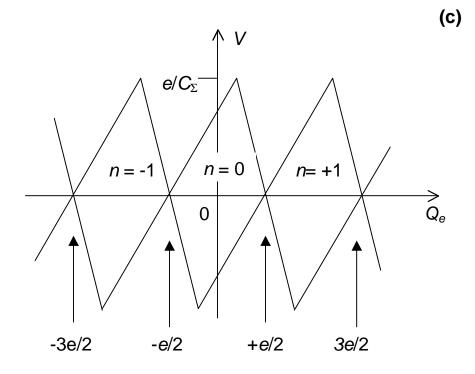

### B. Single-electron Transistor

The latter drawback may be easily corrected by splitting the tunnel junction of the singleelectron box and applying a dc voltage V between the two, now separate, parts of the external electrode (Fig. 6a). The resulting "*single-electron transistor*"<sup>9</sup> is probably the most important device in this field. The device is reminiscent of a usual MOSFET, but with two tunnel barriers embedded in a small conducting island, instead of the usual inversion channel.

The expression for the electrostatic energy *W* of the system

$$W = (ne - Q_e)^2 / 2C_{\Sigma} - eV[n_1C_2 + n_2C_1] / C_{\Sigma} + \text{const}$$

(13)

is an evident generalization of Eq. (5). Here  $n_1$  and  $n_2$  are the number of electrons passed through the tunnel barriers 1 and 2, respectively, so that  $n = n_1 - n_2$ , while the total island capacitance  $C_{\Sigma}$  is now a sum of  $C_0$ ,  $C_1$ ,  $C_2$ , and whatever stray capacitance the island may have. The external charge  $Q_e$  is again defined by Eq. (11) and is just a convenient way to present the effect of the gate voltage U.

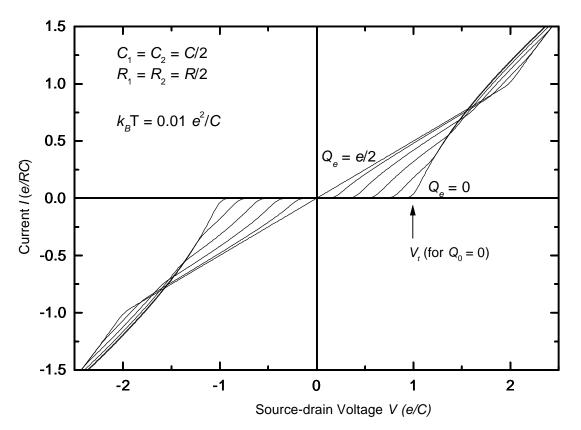

Figure 6b shows typical dc *I-V* curves of this system. At small source-drain voltage *V* there is no current, since any tunneling event would lead to an increase of the total energy ( $\Delta W < 0$ ) and hence according to Eq. (5) at low enough temperatures ( $k_BT << E_c$ ) the tunneling rate is exponentially low. (Cotunneling provides in this region a weak current proportional to  $R_Q^2/R_1R_2$  [20, 21], where  $R_{1,2}$  are the tunnel barrier resistances; as far as  $R_{1,2} >> R_Q$ , this current is small.) This suppression of dc current at low voltages is known as the *Coulomb blockade*.<sup>10</sup>

At a certain *threshold voltage*  $V_t$  the Coulomb blockade is overcome, and at much higher voltages the dc *I-V* curve gradually approaches one of the offset linear asymptotes:  $I \rightarrow (V + \text{sign}(V) \times e/2C_{\Sigma})/(R_1+R_2)$ . On its way, the *I-V* curve exhibits quasi-periodic oscillations of its slope, closely related in nature to the Coulomb staircase in the single-electron box, and expressed especially strongly in the case of a strong difference between  $R_1$  and  $R_2$ .

The most important property of the single-electron transistor is that the threshold voltage, as well as the source-drain current in its vicinity, is a periodic function of the gate voltage, with the period given by Eq. (12). This periodicity is evident from Eqs. (10) and (13): if U is changed by  $\Delta U = e/C_0$ ,  $Q_e$  changes by e, and may be exactly compensated for by one of the electrons tunneling into/from the island. The physical reason for this periodic dependence U (the so-called "*Coulomb* blockade oscillations") is clear from Figs. 5b and 6a: the effect of the gate voltage is equivalent to the injection of charge  $Q_e = C_0U$  into the island and thus changes the balance of the charges at tunnel barrier capacitances  $C_1$  and  $C_2$ , which determines the Coulomb blockade threshold  $V_t$ . In the orthodox theory, the dependence  $V_t(U)$  is piece-linear and periodic (Fig. 6c).

The first successful experimental implementation of the single-electron transistor was carried out by Fulton and Dolan [31], using a relatively simple technique in which two layers of

<sup>&</sup>lt;sup>9</sup> It was invented in 1985 [15, 30], on the background of the earlier work on double-junction systems without the gate [3, 5] and on a similar Cooper-pair system [14].

<sup>&</sup>lt;sup>10</sup> This term was introduced in Ref. 15, but the phenomenon itself had been qualitatively understood much earlier, initially for different systems - see, e.g., Refs. 1, 2.

aluminum are evaporated *in-situ* from two angles through the same suspended mask formed by direct e-beam writing. (This technique, pioneered by G. Dolan [32], has become standard for 100-nm-scale metallic single-electron devices.) Since then single-electron transistors have been demonstrated in numerous experiments using a wide variety of device geometries, materials, and techniques. Of course some of the methods used may be more suitable for future integrated circuit fabrication than others (right now, *none* of them is fast or reproducible enough for VLSI applications). Unfortunately, the paper length restrictions do not allow me to go into any detailed analysis and critical comparison of these techniques, so I will only mention the most important recent trend.

Over the past few years there has been rapid progress in the fabrication of the first transistors with 10-nm-scale islands, with electron addition energies above 10 mV - see Refs. 33-45 and Table 1. The most advanced of these devices, with  $E_a$  beyond ~100 meV, exhibit noticeable Coulomb blockade oscillations at room temperature.<sup>11</sup>

| Materials<br>(Island; Barrier) | Fabrication Method                                          | Highest $E_a$ (meV) | Ref. |

|--------------------------------|-------------------------------------------------------------|---------------------|------|

| Al; AlO <sub>x</sub>           | Evaporation through an e-beam-formed mask                   | 23                  | [39] |

| CdSe; organics                 | Nanocrystal binding to prepatterned Au electrodes           | 60                  | [44] |

| Al; AlO <sub>x</sub>           | Evaporation on a $Si_3N_4$ membrane with a nm-scale orifice | 92                  | [42] |

| Ti; Si                         | Metal deposition on prepatterned silicon substrates         | 120                 | [43] |

| Carboran molecule              | E-beam patterned, thin-film gate; STM electrode             | 130                 | [40] |

| Si; SiO <sub>2</sub>           | E-beam patterning + oxidation of a SIMOX layer              | 150                 | [37] |

| Nb, NbO <sub>x</sub>           | Anodic oxidation using scanning probe                       | 1,000               | [45] |

*Table 1*. Some high- $E_a$  single-electron transistors.

As the transistor island becomes smaller, the effects of energy quantization may become important. The application of the double-index master equations to the single-electron transistor shows that its dc *I-V* curves may be quite complex [50]. However, the situation at small sourcedrain voltage is much simpler. In fact, Fig. 6c shows that on each period of the Coulomb blockade oscillations there is one special point  $Q_e = e(n + 1/2)$ , at which the Coulomb blockade is completely suppressed, and the *I-V* curve has a finite slope at low voltages Fig. 6b). Another way to express the same property is to say that the linear conductance  $G \equiv dI/dV|_{V=0}$  of the transistor as a function of the gate *U* voltage exhibits sharp peaks. Theory shows that even if the electron quantization effects are substantial, the peak position may be found from a very natural "resonance tunneling" condition [9, 50, 51]: an energy level inside the island (with the account of the gate field potential) should be aligned with the Fermi levels in source and drain, which coincide at  $V \rightarrow 0$ . This rule yields a simple equation for the gate voltage distance between the neighboring Coulomb blockade peaks:

$$\Delta U = (\mathcal{C}_{\Sigma} / \mathcal{C}_0) E_a / e. \tag{14}$$

<sup>&</sup>lt;sup>11</sup> Several high  $E_a$  values recorded for bare double-junction systems (without a gate) should also be mentioned [46-49].

If the charging effects dominate  $(E_c \gg E_k)$  this relation is reduced to Eq. (12) of the orthodox theory, but at strong quantization  $(E_k \gg E_c)$  the distance between the Coulomb blockade oscillation peaks, as well as the height  $G_{\text{max}}$  of the peaks, may vary from level to level.

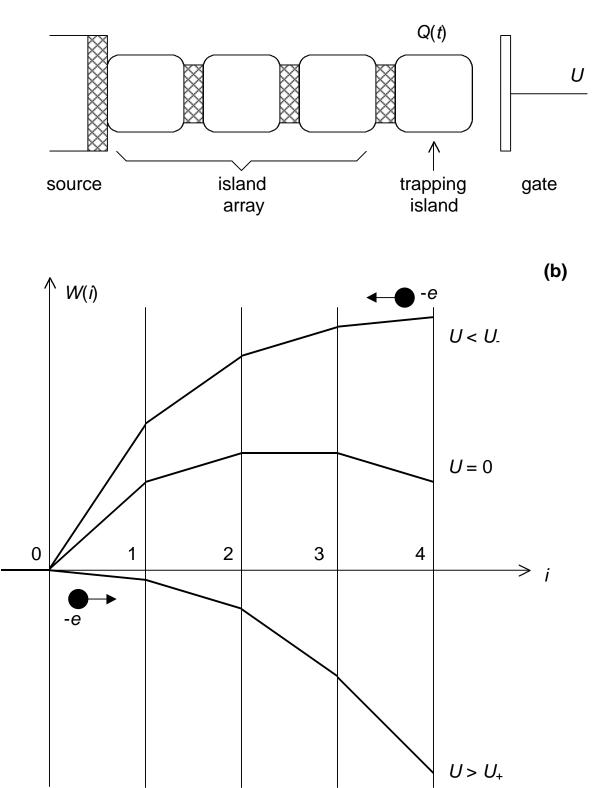

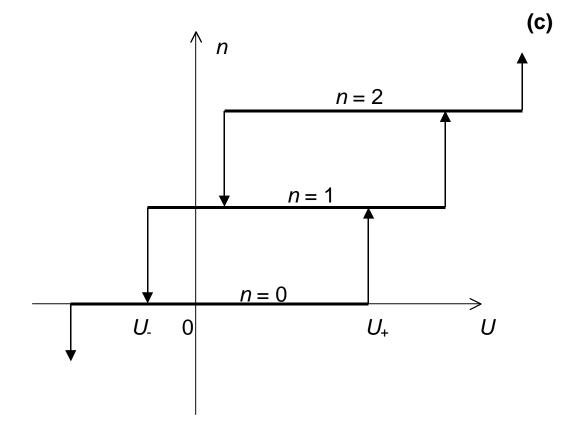

# C. Single-electron Trap

A different generalization of the single-electron box (Fig. 5a) may be obtained by replacing the single tunnel junction with a one-dimensional array of N > 1 islands separated by tunnel barriers (Fig. 7a).<sup>12</sup> The main new feature of this system is its *internal memory* (bi- or multistability): within certain ranges of applied gate voltage U the system may be in one of two (or more) charged states of its edge island.

The reason for this multistability is as follows: due to electric polarization effects an electron located in one of the islands of the array extends its field to a certain distance [16, 55]. In terms of the island numbers, this distance is of the order of

$$M = (C/C_0)^{1/2},$$

(15)

where  $C_0$  is the effective stray capacitance of the island, while *C* is the mutual capacitance between the neighboring islands (usually dominated by that of the tunnel junction). This *"single-electron soliton"* interacts with the array edges (is attracted to them) at a distance of the order of *M*. As a result, the electrostatic self-energy of the soliton has a maximum

$$W_{\text{max}} \approx (e^2/2C) \times \min(M, N/4)$$

(16)

somewhere in the middle of the array (see the middle trace in Fig. 7b). By applying sufficiently high gate voltage  $U = U_+$  the energy profile may be tilted enough to drive an electron into the edge island; if the array is not too long ( $N \le M$ ), other electrons feel its repulsion and do not follow. If the gate voltage is subsequently decreased to the initial level, the electron is trapped in the edge island, behind the energy barrier. In order to remove the electron from the trap, the voltage has to be reduced further, to  $U_- < U_+$  (the upper trace in Fig. 7b). As a result, the n(U) dependence exhibits regions of bi- or multi-stability, in which the charge state of the trap depends on its prehistory (Fig. 7c).

The lifetime of a certain state within the multi-stability region is fundamentally limited by the thermal activation over the energy barrier, and cotunneling [20, 56]. The first effect is exponentially low in  $E_c/k_BT$  (see Eq. (5) and its discussion), while the second effect falls exponentially with the array length N [48, 51]. As a result, electron retention time may be very long [56].

After several preliminary attempts [52, 57], single-electron traps with retention time of at least 12 hours (limited only by the observation time) were successfully demonstrated [58] at low temperatures. Their quantitative characteristics were found [59] to be close to the theoretical predictions, with allowance for the uncertainties of island geometry and randomness of background charge (see Sec. IV.C below). Later similar experiments were carried out by another group [60].

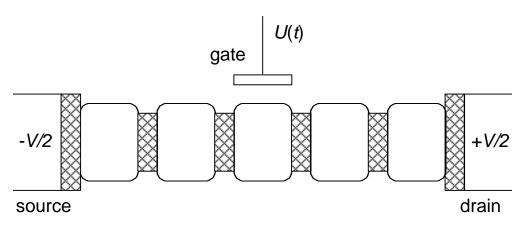

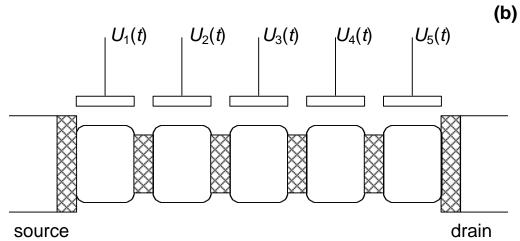

# D. Single-electron Turnstile and Pump

<sup>&</sup>lt;sup>12</sup> To my knowledge, this device was first discussed in 1991 [52, 53], but in fact it may be considered just a particular operation mode of the single-electron turnstile (see Sec. D below) which was invented earlier [54].

Combining both generalizations of the single-electron box, described in Sec. C and D, we naturally arrive at the device shown in Fig. 8a. This "single-electron turnstile" was suggested and demonstrated by a French-Dutch collaboration in 1990 [54]. At V = 0, the device operates exactly like the single-electron trap: one electron may be pulled into the central island (at random, from either source or drain) increasing the gate voltage U beyond a certain threshold; then it may be pushed out by decreasing U. The application of a modest drain-source bias  $V \neq 0$  breaks the source-drain symmetry: now an electron is always picked up from the source when U goes up and delivered to the drain when U goes back down. If the gate voltage is cycled periodically, one electron is transferred from source to drain each period.

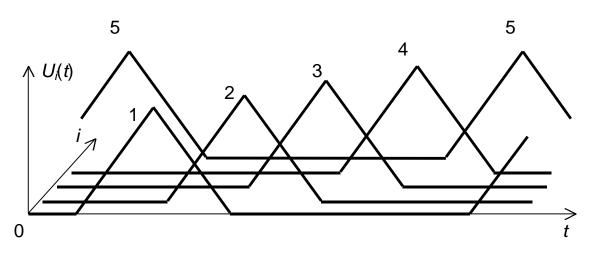

The latter function may be performed even better by another device, the "single-electron pump" ([61], Fig. 8b). Here rf waveforms  $U_i(t)$  applied to each gate electrode are phase-shifted forming a potential wave gliding along the island array. This wave picks up an electron from the source and carries it down to the drain in very much the same way that the charge-coupled devices (see, e.g., Ref. 62) transfer multi-electron bundles. Notice that this device does not need dc source-drain voltage: the direction of the transferred electron is determined by that of the running wave of electric potential.

#### E. SET Oscillators

Much of the initial excitement around single-electron tunneling was induced by the prediction [15] that it could be used to generate narrowband oscillations with a frequency fundamentally proportional to dc current:

$$f_{\rm SET} = I/e. \tag{17}$$

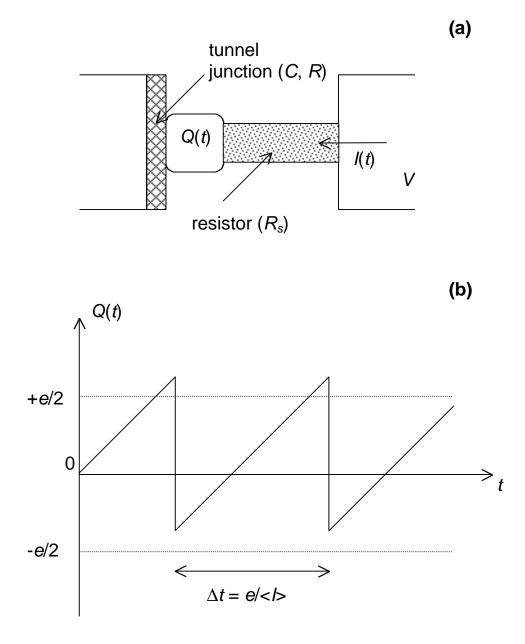

Conceptually, the simplest system capable of proving these "*SET*" (from "single-electron tunneling") oscillations may be formed from a single-electron box (Fig. 5a) by replacing the capacitance  $C_0$  with an Ohmic resistor  $R_s$  that satisfies the following requirement:

$$R_{s} \gg R_{Q}. \tag{18}$$

Figure 9a shows the resulting simple device, while Fig. 9b illustrates its dynamics. Theory says that SET oscillations should arise as soon as applied dc voltage *V* exceeds the Coulomb blockade threshold  $V_t = e/2C$  and gradually disappear in background shot noise at  $I \ge 0.1e/RC$ . Experimental implementation of this device is not, however, easy for the following reason.

The theory of SET oscillations implies that what we call the Ohmic resistor provides a *continuous* transfer of charge, i.e. is capable of transferring sub-single-electron amounts of electricity in order to recharge the island capacitance in time intervals between the subsequent tunneling events (Fig. 7b). This assumption, though seemingly counterintuitive, is supported by the observation that the macroscopic diffusive conductors do not exhibit shot noise at voltages  $V > k_BT/e$ , as should happen at the discrete transfer of electrons (and as really happens, e.g., in tunnel junctions). The theoretical explanation of the continuous conduction in such conductors is based on the extended character of the electron - see, e.g., Ref. 7. For the implementation of a narrowband SET oscillator, however, the Ohmic resistor has to combine the continuous transfer of charge with very high resistance (~1 M $\Omega$  or higher) and very small stray capacitance (~ $C <<e^2/k_BT$ ).

After a decade-long effort by several groups [63-69], this goal has been only partly met: continuous transport was demonstrated in ultra-thin-film strips with specific resistance up to about

10 k $\Omega/\mu$ m, i.e.  $R_s \sim 10^5 \Omega$  for 10- $\mu$ m-scale length which gives a still acceptable capacitance for sub-1-Kelvin experiments. The resulting range  $R_s/R_{\varrho}$  is too small to satisfy the strong conditions (18); this is why only questionable evidence of SET oscillations in a single-junction system has been obtained [64]. (The SET oscillations with frequency expressed by Eq. (17) were observed more reliably although indirectly [70] in 1D junction arrays which may provide quasi-sub-electron transport of charge [16, 71].)

# F. Superconductor Systems

In systems with superconducting electrodes the single particle charging effects may be more complicated. What follows is a list of the major new features:

1). The seed dc *I-V* curve of a single junction, which participates in Eq. (5), may be very nonlinear even at small (millivolt - scale) voltages, due to superconducting energy gap  $\Delta$  in the density of states - see, e.g., Chapter 3 of Ref. [72]. In particular, due to this feature, the charge sensitivity of single-electron transistors with superconducting electrodes may be considerably better than in the normal state [73].

2). If a superconducting island has an even total number of electrons, at low temperatures  $(k_BT << \Delta)$  they are all bound into Cooper pairs. This is why the addition of a new, odd electron requires the energy  $E_a + \Delta$ , while the addition of the next, even electron, takes  $E_a - \Delta$ . These "*parity effects*" predicted in 1992 [74] and repeatedly observed experimentally (see, e.g., Refs. 75-77) may substantially affect the dynamics of single-electron devices.

3). If the normal resistance of a tunnel barrier is relatively low,  $R \leq (\Delta/E_c)R_o$ , the combination of charging and Josephson coupling makes tunneling of *single Cooper pairs* possible. Since Cooper-pair tunneling is always elastic, its properties differ considerably from that of single electrons. For example, the superconducting versions of single-electron devices may have quantized energy levels [14]; this level structure has been observed in recent experiments [78, 79] with so-called *Bloch transistors*, i.e. Cooper-pair analogs of single-electron transistors, see Fig. 6a.<sup>13</sup> Another important property of the Bloch transistor is that it may exhibit a finite source-drain supercurrent with amplitude being a 2*e*-periodic function of  $Q_e$ . This prediction [80, 81] has been confirmed in numerous experiments - see, e.g. Ref. 82. In resistively-coupled superconductor devices (such as that shown in Fig. 9a) the Cooper-pair tunneling may result in the generation of so-called "*Bloch oscillations*" [14] with frequency

$$f_{\rm B} = I/2e. \tag{19}$$

either instead of or on top of the SET oscillations. These oscillations (which present a dual quantum-mechanical analog of the usual Bloch oscillations in solids, see, e.g., Ref. 83) have been observed experimentally [63].

# **IV. ANALOG APPLICATIONS**

A. Supersensitive Electrometry

<sup>&</sup>lt;sup>13</sup> Bloch transistor was first suggested and analyzed in 1986 [80, 81].

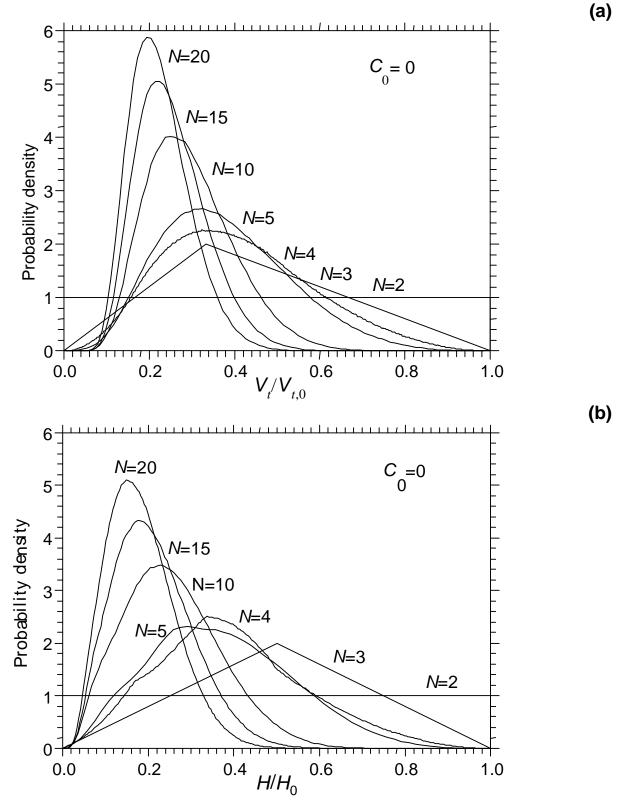

If the source-drain voltage V applied to a single-electron transistor is slightly above its Coulomb blockade threshold  $V_i$ , source-drain current I of the device is extremely sensitive to the gate voltage U. In fact, Fig. 6b shows that even the changes  $\delta U$  corresponding to sub-singleelectron variations  $\delta Q_e$  of the external charge lead to measurable variations of I. This extremely high sensitivity has been suggested [30] as a basis for supersensitive electrometry. Calculations based on the orthodox theory have shown [84] that the sensitivity of such an electrometer is not very impressive if the internal capacitance  $C_i$  of the signal source is large on the scale of  $e^2/k_BT$  (at sub-1-K temperatures, above ~ 0.1 pF). On the other hand, if the source is so small and so close to the single-electron transistor that  $C_i$  of the order of the capacitances of the transistor  $C_{1,2}$ , white noise limits the charge sensitivity at an extremely low level,  $(\delta Q_e)_{\min}/\Delta f^{1/2} < 10^{-5} e/\sqrt{Hz}$ , for the devices with routinely achieved 100-nm-scale islands (here  $\Delta f$  is the measurement bandwidth).

Since the technology of fabrication of tunnel barriers for single-electron devices is still in its infancy, they apparently contain many electron trapping centers and other two-level systems "telegraph noise" - random low-frequency variations of the barrier capable of producing conductance. This may explain the fact that the excess 1/f-type noise resulting from these variations exceeds [85] the fundamental white noise up to very high frequencies (apparently at least a few MHz). Only in high-frequency experiments [86] has the white noise been observed (and shown to vary in accordance with the theoretical predictions). This is why the best charge resolution obtained at relatively low frequencies (~10 Hz) was somewhat lower than  $10^{-4} e/\sqrt{\text{Hz}}$  [87-89]. Nevertheless, even with this "high" noise, these electrometers are some 6 orders of magnitude more sensitive that the best commercially available instruments, and about 100 times more sensitive than specially designed low-temperature semiconductor devices (see, e.g., Ref. 90, 91). In a very recent work [92] in which GHz-range modulation was used to get away from a part of the 1/f noise, a charge sensitivity close to  $10^{-5}e/\sqrt{\text{Hz}}$  (at ~1 MHz) was demonstrated. This result gives hope that electrometers with the white-noise-limited sensitivity (~ $10^{-5}e/\sqrt{\text{Hz}}$  at helium temperatures and ~ $10^{-5}e/\sqrt{\text{Hz}}$  $^{4}$  e/ $\sqrt{\text{Hz}}$  at room temperatures) will be routinely available in the near future<sup>14</sup>.

The high sensitivity of single-electron transistors has already enabled several groups to use them as electrometers in unique physical experiments. For example, they have made possible unambiguous observations [75-77] of the parity effects in superconductors, mentioned in Sec. II.G above. Absolute measurements of extremely low dc currents ( $\sim 10^{-20}$  A) have been demonstrated [94]. The transistors have also been used in the first measurements of single-electron effects in single-electron boxes [29] and traps [52, 57-60]. A modified version of the transistor has been used for the first proof of the existence of fractional-charge excitations in the fractional quantum Hall effect [95]. Another recent example is the sensitive measurement of local variations in the chemical potential of 2D electron gas in GaAs/AlGaAs heterostructures [96, 97]. Further application of these unique electrometers in scientific experimentation is certainly imminent.

Finally, a new exciting field has been opened by the work of a Lucent Technologies group [98] who have managed to fabricate a single-electron transistor on the tip of a scanning probe and with its help implement a new type of scanning microscopy, combining submicron spatial resolution with sub-single-electron sensitivity. This novel technique has already been used to observe single charged impurities in GaAs/AlGaAs heterostructures.

<sup>&</sup>lt;sup>14</sup> Another important trend is the integration of single-electron transistors with field-effect transistors providing the next amplification stage, and more importantly the matching of the very high output impedance of the SET to that of usual RF transmission lines. This allows the useful bandwidth of the single-electron transistor electrometers to be raised to tens MHz - see, e.g., Refs. 89, 93.

# B. Single-electron spectroscopy

Another useful spin-off of single-electron electrometry is the possibility of measuring the electron addition energies (and hence the energy level distribution) in quantum dots and other nanoscale objects, pioneered by M. Kastner's group at MIT [99].

There are two natural ways to carry out such measurements. The first is to use the quantum dot as the island of the single-electron box, capacitively coupled to the single-electron transistor or other sensitive electrometer [90, 100]. The second is to use the quantum dot directly as the island of a weakly biased single-electron transistor ( $V \rightarrow 0$ ), and measure the gate voltages  $U_n$  providing the sharp increase of the source-drain conductance G - see Eq. (14) and its discussion. The latter method is technically simpler (only one small island is needed) and is preferred by most groups. Moreover, the height of the conduction peak gives additional information on the corresponding electron wavefunction distribution in the dot (see, e.g., Refs. 90, 101).

Single-electron spectroscopy was first applied to laterally-confined "puddles" of 2D electron gas in semiconductor heterostructures with lateral [102] or vertical [103] tunneling to source and drain. Recently, this technique was also used to study electron addition spectra of nanometer metallic particles [42, 104], naturally formed nanocrystals [44, 105], C<sub>60</sub> buckyballs [46], and carbon nanotubes [106, 107], with good prospects to have it extended to numerous nanoobjects, first of all organic macromolecules and clusters [40, 47, 49]. Presently single-electron spectroscopy is developing virtually independently of other applications of single-electronics. This is why I will make no attempt to review it in any detail; for recent reviews the reader is referred, e.g., to Ref. 12. I would like, nevertheless, to offer one remark.

Most of the semiconductor quantum dots studied experimentally by single-electron spectroscopy have shown that their energy spectra are irreproducible and only distantly related to those of the idealized simple objects studied in most theoretical works. This is quite understandable taking into account the fact that the dots have numerous electron scattering centers and/or shape irregularities. (These objects are sometimes called "*artificial atoms*", but so far these atoms are certainly not as tidy as the natural ones.) In the presence of uncontrollable inhomogeneities, the only available approach to sort out single-electronics data is statistical. The few past years were marked by rapid experimental and theoretical progress in this direction, especially after it was recognized that in some cases the results may be adequately described by the well-developed random matrix theory - see, e.g., Ref. 108.

This progress should not conceal the fact that there is very little chance of practical application of single-electron devices with random electron addition energies, especially in integrated circuits (see Sec. V below). In this context the only hope is that better nanofabrication techniques will give us more reproducible structures in future. The recent unique experiments by S. Tarucha, L. Kouwenhoven and their collaborators [109] gave the first evidence of a semiquantitative agreement between the experiment and quantum calculations assuming a simple dot geometry, presumably indicating that reproducible quantum dots may eventually be possible after all. Unfortunately, even that would hardly solve the related problem of random background charges - see Sec. V.C below.

# C. DC Current Standards

Another possible application of single-electron tunneling is fundamental standards of dc current. The initial suggestion for such a standard [14, 15] was to phase lock SET oscillations (17)

or Bloch oscillations (19) in a simple oscillator (Fig. 9), with an external rf source of a well characterized frequency f. The phase locking would provide the transfer of a certain number m of electrons per period of external rf signal and thus generate dc current which is fundamentally related to frequency as I = mef. Later it turned out to be more convenient to use such a stable rf source to drive devices such as single-electron turnstiles and pumps (see Sec. III.E above), which do not exhibit coherent oscillations in the autonomous mode.

Already the first experiments [54] with the 2+2-junction turnstile have shown that its relative accuracy  $\delta I/I$  can be as good as ~10<sup>-3</sup>. The following theoretical work [110-113] has indicated that even better accuracy may be provided by the pumps, since these devices allow a more gentle transfer of the single-electron along its array, and leave less margin for the parasitic processes of thermal activation and cotunneling which may result in error (say, the occasional transfer of an extra electron). An additional advantage of the pump is the possibility of compensating for the random background charge of each island (see below) with a specially tuned dc voltage bias applied to each gate. Theory indicates [113] that the known effects limit the accuracy of a 5-junction turnstile with typical present-day parameters and waveforms at the level of ~10<sup>-12</sup> at *f*~10 MHz, and even down to 10<sup>-16</sup> if special waveforms are used.

The best experimental effort so far gave an accuracy of  $1.5 \times 10^{-8}$  [114], presumably limited by the photo-excitation of extra electrons by some multi-GHz electromagnetic radiation creeping into the system. Though finding and mending these radiation leaks may present a problem, apparently it can be solved as evidenced by the above-mentioned experiments with single-electron traps [58, 60]. Thus I have no doubt that a dc current standard with relative accuracy better than 10<sup>-10</sup> (sufficient for all the suggested applications - see, e.g., Ref. 115) can be implemented using pump-type devices.

A greater challenge is a substantial increase in the output current of single-electron standards (presently in the pA range) which would allow much broader application of these devices in metrology. A direct increase of the drive frequency f in pump-type devices runs into the problem of rapidly growing dynamic error rate, as soon as it becomes comparable to 1/RC [111-113]. One way to avoid this problem is to use a single-Cooper-pair version of the pump; here tunneling is elastic, and the drive frequency may be much higher, eventually limited only by the energy gap of the superconducting materials used at a few tens GHz ( $I = ef \sim$  few nA). Unfortunately, these devices are still plagued with the occasional quasiparticle "poisoning", the possible reasons for which are not well understood - see, e.g., Ref. 74.

Another way may be getting rid of the tunneling altogether. In fact, instead of waiting until an electron tunnels through a barrier separating two islands of a pump, it would be much better to carry it over, trapped in a potential well moving along a solid state structure, just as is done with multi-electron bundles in charge-coupled devices [62]. An interesting attempt to implement such a structure using surface-acoustic waves in a GaAs channel is described in Ref. 116. I believe, however, that a more straightforward way would be a direct scaling down of electric-fieldcontrolled silicon-based CCD structures, simultaneously with their cooling to sub-Kelvin temperatures (which may require an increase of electrode doping levels to avoid carrier freeze-out). To my knowledge, this approach has not yet been explored.

#### D. Temperature Standards

Recently, an unexpected avenue toward a new standard of absolute temperature has been developed by J. Pekola and his collaborators [117-119], on the basis of 1D single-electron arrays.

At low temperatures, arrays with N >>1 islands exhibit dc *I-V* curves generally similar to those of single-electron transistors (see, e.g., Fig. 6b), with a clear Coulomb blockade of tunneling at low voltages ( $|V| < V_i$ ) and approaching the linear asymptote V = NRI + const at  $|V| >> V_i$ . If the temperature is raised above  $E_c/k_B$ , thermal fluctuations smear out the Coulomb blockade, and the *I*-*V* curve is almost linear at all voltages:  $G \equiv dI/dV \approx G_n \equiv 1/NR$ . The only remaining artifact of the Coulomb blockade is a small dip in the differential conductance around V=0, with amplitude  $\Delta G/G_n \approx - E_c/6k_BT$  and the FWHM width

$$\Delta V = 5.44 \ Nk_{\rm B}T/e. \tag{20}$$

Theoretical analysis based on the orthodox theory has shown [118, 119] that equation (20) is surprisingly stable with respect to almost any variations of the array parameters (with the important exception of a substantial spread in the junctions' resistances), providing a remarkable opportunity to use the arrays for absolute thermometry, since the fundamental constants are known with high accuracy. Each particular array may give high (~1%) accuracy of *T* within less than one decade of temperature variations, but for arrays with different island size (and hence different  $E_c$ ) these ranges may be shifted and overlap. Thus it is possible to have an absolute standard of temperature with a very broad (say, two-decade) total range from several circuits fabricated on a single chip.

This development is very encouraging, but since all this work is recent, some time is needed to see whether these new devices will be able to compete with (or even replace) the established temperature standards.

#### E. Resistance Standards

According to a theoretical prediction [80, 81], in the resistively-biased Bloch transistor, Bloch oscillations (19) may coexist with the usual Josephson oscillations with frequency

$$f_{\rm J} = 2eV/h. \tag{21}$$

Moreover, these two oscillations may phase lock, resulting in the fundamental quantization of the off-diagonal component of the conductance matrix of this three-terminal device:

$$R_{\perp} = V/I = (m/n)(h/e^2),$$

(22)

where m and n are small integers. A more practical way to the same relation may be the simultaneous phase locking of both the Bloch and Josephson oscillations with the same external microwave source.

Relation (21) is similar to that taking place at the quantum Hall effect and promises even higher fundamental accuracy. This phenomenon has not yet been explored experimentally, because the implementation of narrow-band Bloch oscillations requires micron-scale resistors with  $R_s \sim 1$ M $\Omega$ , which are still at the developmental stage. However, very recent results in this direction [69] are encouraging.

# F. Detection of Infrared Radiation

The first calculations [120] of the videoresponse ("photoresponse") of single-electron systems to electromagnetic radiation with frequency  $f \sim E_c/h$  have shown that generally the response differs from that following from the well-known Tien-Gordon theory [121] of photon-assisted

tunneling. In fact, this famous result is based on the assumption of independent (uncorrelated) tunneling events, while in single-electron systems the electron transfer is typically correlated. Nevertheless, further work [122] has shown that the Tien-Gordon formula *is* applicable to the individual tunneling *rates*:

$$\Gamma(\Delta W, A) = \sum_{k=-\infty}^{\infty} J_k^2 (eA/hf) \times \Gamma(\Delta W + khf, 0).$$

(23)

where *A* is the amplitude of the microwave voltage across the junction, *f* is the radiation frequency, while  $J_k(x)$  are the first-order Bessel functions of argument *x*. This formula is believed to be valid for any system which may be described with master equations similar to Eq. (7), regardless of the exact formula for the background tunneling rate  $\Gamma(\Delta W, 0) \equiv \Gamma(\Delta W)$ . Moreover, for most important interesting cases, e.g. near the Coulomb blockade threshold, Eq. (23) is also valid for the dc current as a whole. These predictions have been confirmed experimentally - see, e.g., Refs. 122-124.

This fact implies that single-electron devices, especially 1D multi-junction arrays with their low cotunneling rate, may be used for ultrasensitive video- and heterodyne detection of high-frequency electromagnetic radiation, similar to the superconductor-insulator-superconductor (SIS) junctions and arrays (see, e.g., Refs. 125, 126). The single-electron arrays may have two advantages over their SIS counterparts: lower shot noise (because the Coulomb blockade in systems with N >> 1 islands in series may provide lower leakage currents than the superconducting energy gap), and convenient adjustment of the threshold voltage (by changing the junction size and hence  $E_c$ ). This opportunity is especially promising for detection in the few-terahertz frequency region, where no background-radiation-limited detectors are yet available.

A major obstacle on the path toward the extension of this approach to imaging may be the randomness of the background charge (see Sec. V.C below) which may make capacitive gating of each island necessary. This may be acceptable for single detectors, but not for multiple-pixel focal-plane arrays.

Another interesting opportunity is the use of single-electron transistors as pre-amplifiers and/or single-electron counters for semiconductor infrared detectors - see experiments [94].

# V. PROSPECTS FOR DIGITAL APPLICATIONS

Most of the opportunities described in the previous section are very promising, but in terms of contemporary electronics as a whole they still look like niche applications. From the very formulation of single-electronics as an applied discipline [6, 30, 127], the most intriguing question was whether single-electron devices will be able to compete with semiconductor transistor circuits in mainstream, digital electronics. Several paths toward this goal have been explored.

# A. Voltage State Logics

The first opportunity [30] is to use single-electron transistors (Fig. 6a) in the "voltage state" mode. In this mode, the input gate voltage U controls the source-drain current of the transistor which is used in digital logic circuits, similarly to the usual field-effect transistors (FETs). This means that the single-electron charging effects are confined to the interior of the transistor, while externally it looks like the usual electronic device switching multi-electron currents, with binary unity/zero presented with high/low dc voltage levels (physically not quantized). This concept

simplifies the circuit design which may ignore all the single-electron physics particulars, except the specific dependence of the source-drain current I on voltages V and U - see Fig. 6b,c.

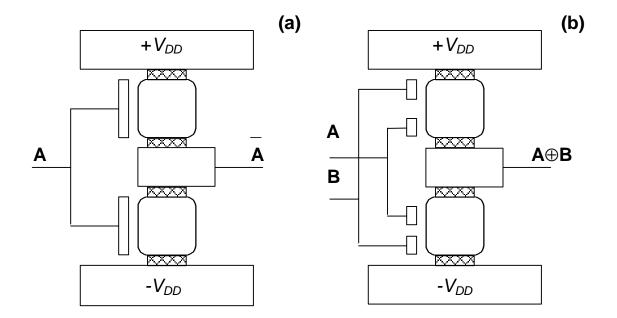

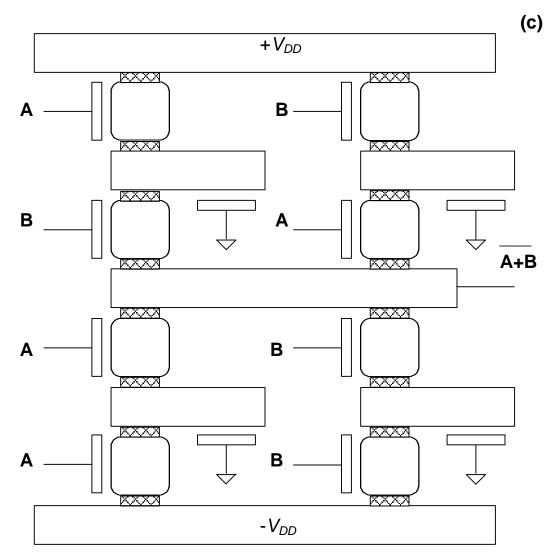

For a digital circuit designer, there is both good and bad news in this dependence. On the one hand, the alternating transconductance of the single-electron transistor (Fig. 6c) makes possible a very simple design of complementary circuits using transistors of just one type [30, 128]<sup>15</sup>. On the other hand, it makes the exact copying of CMOS circuits impossible, and in order to get substantial parameter margins, even the simplest logic gates have to be re-designed. The re-designed and optimized circuits (Fig. 10) may operate well within a relatively wide parameter window [130]. However, their operation range starts shrinking under the effect of thermal fluctuations as soon as their scale  $k_B T$  reaches approximately  $0.01E_a$  [130]. (For other suggested versions of the voltage state logic [128, 131], the temperature range apparently is even narrower). The maximum temperature may be increased by replacing the usual (single-island, double-junction) single-electron transistors for short 1D arrays with distributed gate capacitances [132]. For example, 5-junction transistors allow a 3-fold increase of  $T_{max}$ , for the price of bulkier circuits. However, according to Fig. 2, in order to operate at room temperature even with this increase the transistor island size has to be extremely small (<1 nm).

One more substantial disadvantage of voltage state circuits is that neither of the transistors in each complementary pair is closed too well, so that the static leakage current in these circuits is fairly substantial, of the order of  $10^{-4} e/RC$ . The corresponding static power consumption is negligible for relatively large devices operating at helium temperatures. However, at the prospective room-temperature operation this power becomes on the order of  $10^{-7}$  Watt per transistor. Though apparently low, this number gives an unacceptable static power dissipation density (>10 kW/cm<sup>2</sup>) for the hypothetical circuits which would be dense enough (>10<sup>11</sup> transistors per cm<sup>2</sup>) to present a real challenge for the prospective CMOS technology.

# B. Charge State Logics

The latter problem may be avoided by using another type of logic device in which single bits of information are presented by the presence/absence of single electrons at certain conducting islands *throughout the whole circuit*. In these circuits the static currents and power vanish, since there is no dc current in any static state.

This approach was first explored theoretically in 1987 [133]. In the suggested circuits an extra electron could be propagated along considerable externally-timed shift-register-type segments of the circuit, while resistively-coupled transistors provided splitting of the signal and binary logic operations. Unfortunately the suggested circuits required resistors and also had very narrow parameter margins. Since then, several families of charge state logics have been suggested - see, e.g., Refs. 134-150. Some of them [138, 141, 147] have developed further the initial concept of electron propagation [133], but using more practical, capacitively-coupled circuits. In most suggestions, however, the electron is confined in a cell consisting of one or a few islands, while the logic switching is achieved via electrostatic [134-137, 140, 142, 144-148, 150] or spin [139, 143,149] coupling of the cells.

A deeper classification of single electron logics may be based on where they take the energy necessary for logic operations: from dc power supply [133, 134, 141, 147], ac power supply

<sup>&</sup>lt;sup>15</sup> This is true for both resistively-coupled [30] and capacitively-coupled [128] transistors. Unfortunately, the resistively-coupled devices are more sensitive to thermal fluctuations [129] (on top of the difficulties with implementation of small resistors - see below).

(also playing the role of global clock) [134, 140, 142, 145], or just from the energy of an external signal [135-139, 143-146, 149, 150]. The latter category of devices implies the use some (typically unspecified) inter-stage amplifiers in order to compensate for the energy lost inside the logic stages.<sup>16</sup>

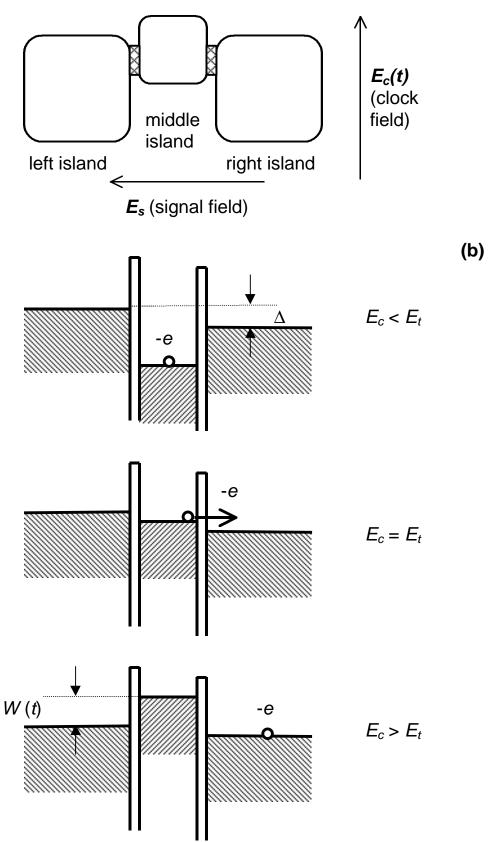

Only a few of these concepts have been analyzed in detail, especially at finite temperatures. To my knowledge, the most robust single-electron logic circuits suggested till now are those based on the so-called "SET Parametron" [142]. The simplest version of the device uses three small islands separated by two tunnel barriers (Fig. 11a). The central island is slightly shifted out of the center line. A periodic "clock" electric field  $E_c$  keeps an extra electron in the central island during a part of the clock period. At some instant, the electron transfer to one of the edge islands becomes energy advantageous (the sign of  $\Delta W$  changes from negative to positive). If the system were completely symmetric, the choice between the two edge islands would be random, i.e. the system would undergo what is called spontaneous symmetry breaking. However, even a small additional field  $E_s$  applied by a similar neighboring device(s) may determine the direction of electron tunneling at the decision-making moment. Once the barrier  $\Delta W$  created by the further change of the clock field has become large enough, the electron is essentially trapped in one of the signal field  $E_s$  for the neighboring cells. The sign of this field (i.e. of the electric dipole moment of the device) presents one bit of information.

Figure 11c shows a shift register based on SET Parametrons. The direction of the shift of the central island of each next device is shifted by  $\pi/3$  within the yz plane. The circuit is driven by electric field  $E_c(t)$  rotating in the same plane and providing the periodic switching on the SET parametrons, with an appropriate phase shift. As a result, each digital bit (one per three cells) is being shifted by 3 cells along the structure each clock period. Logic gates may be implemented in the same way [142]. Geometric modeling and numerical simulation of these circuits within the framework of the orthodox theory have shown that they may operate correctly within approximately  $\pm 20\%$  intervals of clock amplitude. Estimates show that the maximum operation temperature of these logic circuits is of the order of that of voltage mode circuits, i.e. of the order of  $0.01E_c/k_B$ , if the bit error rate is in the practically acceptable range (below  $\sim 10^{-20}$ ).

A new, potentially useful feature of the charge state logics is the natural internal memory of their "logic gates" (more proper terms are "finite-state cells" or "timed gates"), thus combining the functions of combinational logic and latches. This feature (very similar to that of the ultrafast RSFQ logic [151]) makes natural the implementation of deeply pipelined and cellular automata architectures. The main disadvantage of these circuits in comparison with voltage state logic is the lack of an effective means of transferring a signal over large distances: crudely speaking, this technology does not allow simple wires, just shift registers.

I should also mention in passing the recent proposals [152-155] to use single-electron or single-Cooper-pair structures for quantum computing. These proposals are so new that they should be analyzed in much more detail before any judgement is rendered. The only comment I can offer at this stage is that the practical implementation of these devices would be even harder than the "classical" charge state logics, since quantum computing also requires a high degree of coherence of the charge (or spin) states to be maintained.

# C. Problems, Problems...

<sup>&</sup>lt;sup>16</sup> Some of these proposals are highly controversial - see, e.g., the discussion in Refs. 140, 148-150.

The first big problem with all the known types of single-electron logic devices is the requirement  $E_c \sim 100 k_B T$ , which in practice means sub-nanometer island size for room temperature operation (Fig. 2).<sup>17</sup> If we are not just talking about single-device demos but VLSI circuits, this fabrication technology level is still nowhere in sight. Moreover, even if these islands are fabricated by any sort of nanolithography, their shape will hardly be absolutely regular. Since in such small conductors the quantum kinetic energy gives a dominant contribution to the electron addition energy ( $E_k >> E_c$ , see Fig. 2), even small variations in island shape will lead to unpredictable and rather substantial variations in the spectrum of energy levels and hence in the device switching thresholds.

We may dream, of course, about using some naturally made, reproducible objects such as  $Au_{55}$  clusters, or  $C_{60}$  buckyballs, or some other macromolecules. (Fortunately, single-electronics imposes no fundamental restrictions on the island material, besides being "conductive", i.e. having no excessive energy gaps around the Fermi level). It must not be forgotten, however, that these objects have to be aligned with other islands and possibly conducting nanowires, and separated from them by tunnel barriers with well-reproducible capacitances and tunnel resistances. The much-advertised "self-assembly" (which nowadays means mostly the formation of uniformly packed 2D arrays of clusters or macromolecules) is not enough! The research in this area should eventually address the issue of island placement on the preliminarily defined points with nanometer precision, and I have not heard about any simple solution to this problem.<sup>18</sup>

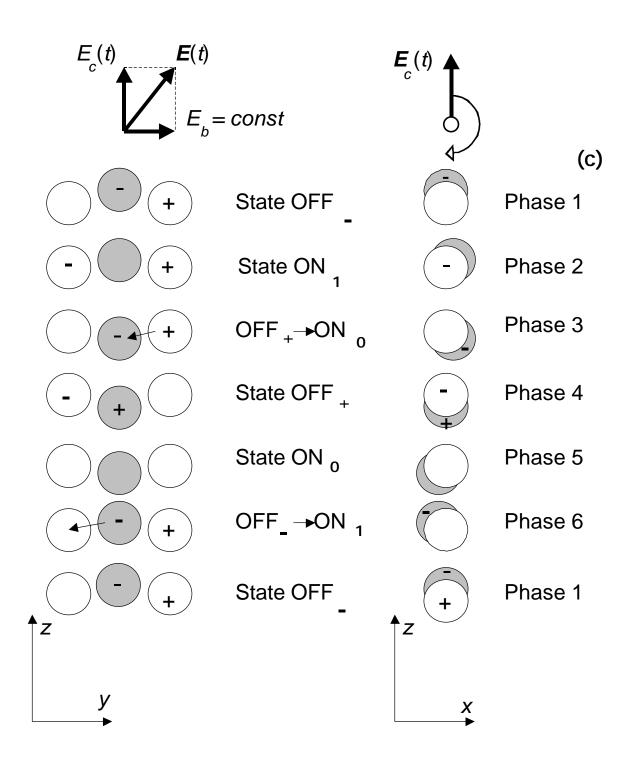

The second major problem with single-electron logic circuits is the infamous *randomness* of the background charge. Figure 12 illustrates this problem with the example of the single-electron transistor. Let a single charged impurity be trapped in the insulating environment, say on the substrate surface, at a distance *a* from the island, comparable to its size. The impurity will polarize the island, creating on its surface an image charge  $Q_0$  of the order of *e*. This charge is effectively subtracted from the external charge  $Q_e$  (see Eq. (11)) which determines the Coulomb blockade thresholds  $V_i$ . As is evident from Fig. 6b,c, this shift may be large, of the order of  $(V_i)_{max}$ , even from a simple impurity. Using a very optimistic estimate of  $10^{10}$  cm<sup>-2</sup> for the minimum possible concentration surface/interface charge trap concentration (see, e.g. Ref. 156), and assuming that the minimum device density of practical interest is  $10^{10}$  cm<sup>-2</sup>, we get that about one of 1,000 devices with 1-nm islands will have a considerable background charge fluctuation ( $|Q_0| > 0.1 e$ ).<sup>19</sup> Presumably, this is unacceptable for any VLSI application.

There is a slight chance that this problem (which is dominant in present-day experiments with relatively large devices) will just go away when the islands are scaled down to sub-nanometer size. In fact, the same image charge  $Q_0$  which causes all the trouble always attracts the initial impurity with the Coulomb force scaling as  $a^2$ . If this force exceeds the impurity pinning force, it will diffuse toward the particle and finally fall out on its surface where it is no longer dangerous (at this point, Q becomes equal to e and is immediately compensated by one of the tunneling

<sup>&</sup>lt;sup>17</sup> I do not believe that any practical advantage these circuits may offer would ever justify their cooling to helium (or lower ) temperatures.

<sup>&</sup>lt;sup>18</sup> The electrostatic trapping technique described in Ref. 49 is certainly interesting, but it is not clear how it could be extended to integrated circuits.

<sup>&</sup>lt;sup>19</sup> Devices with vertical transport are less sensitive to charge impurities located at relatively large distances, because of electrostatic screening by external electrodes [157]. For room temperature operation, however, the cross-section area of these structures should be so small (comparable to the square of the tunnel barrier thickness), that the screening would not be substantial.

electrons). Since some evidence of such "self-cleaning" has been noticed even for particles with  $a \sim 100$  nm [4, 158], this process may become quite effective at  $a \sim 1$  nm. Unfortunately, I am not aware of any detailed experimental study of this problem, despite the fact that its crucial importance for applications has been discussed in the literature at least since 1992 [53].

Another possibility is to look for single-electron logic devices which would be insensitive to the background charge. I know of two such proposals: the voltage stage logic based on resistivelybiased single-electron transistors [30] and an rf-parametron-type logic based on mutual phase locking of SET oscillators [159]. Both these suggestions rely on Ohmic resistors with continuous (or at least quasi-continuous) transfer of charge which would provide the compensation for the fractional part of the random background charge. The implementation of these resistors for room temperature operation would, however, be very difficult. In fact, theoretical analyses [160, 161] show that in order to provide the continuous transfer of charge a diffusive conductor has to be much longer than the electron-phonon interaction length. For silicon, which is a primary candidate material for these resistors, this length is of the order of 30 nm (see, e.g., Ref. 162), i.e. much larger than the desirable size of the whole device. Moreover, the stray capacitance of such a resistor would be much larger than that of the island itself, dramatically reducing its charging energy and hence the maximum operation temperature.

All these problems put the very idea of using single-electron devices for logic functions very much in doubt. In addition, even if this logic is implemented, it will hardly be extremely fast, because of the high output impedance of single-electron devices ( $Z \sim R \gg R_{\varrho} \sim 10 \text{ k}\Omega$ ). For example, the charging time of an interconnect as short as 100 µm through a 100 k $\Omega$  impedance is of the order of 1 ns, which is hardly an exciting speed. Finally, the fields in which the greatest asset of single-electron devices, their potentially enormous density, are most needed, are not logic but rather random access memories and long-term data storage systems. Fortunately, these are precisely the fields in which encouraging ideas have emerged during the past few years.

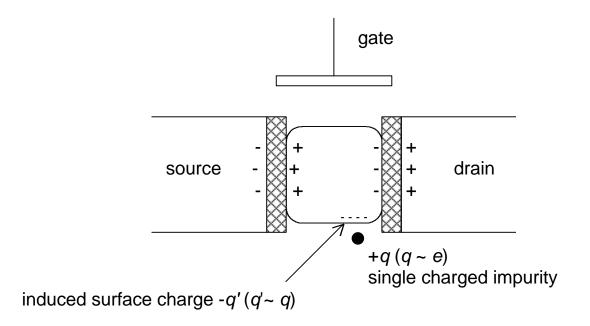

#### D. Background-Charge-Insensitive Memory

Generally speaking, the single-electron trap (Fig. 7a) complemented by an electrometer for sensing its charge state, may already be considered a memory cell with non-destructive readout (NDRO). However, due to the background charge randomness, the 1D array of small islands used in the trap is not a perfect circuit component for the transfer of single electrons. Figure 13 shows the statistical distribution of the Coulomb blockade threshold and the energy barrier height of such arrays, calculated with the assumption of the random background charge of each island. It is evident that these statistics are not good enough for VLSI circuits: even if the junctions are exactly similar there is a considerable chance that the Coulomb blockade will be almost completely suppressed, and hence the memory cell incapable of keeping an electron inside. (The situation with randomly shaped arrays is even worse: the two tunnel junctions with highest resistances typically define the electron transport, effectively turning the array into a single-electron transistor with its relatively high cotunneling rate - see, e.g., the experimental results in Ref. 163). The background charge also makes the single-electron transistor readout unreliable: a random charged impurity may easily imitate the electron trapped in the memory cell.

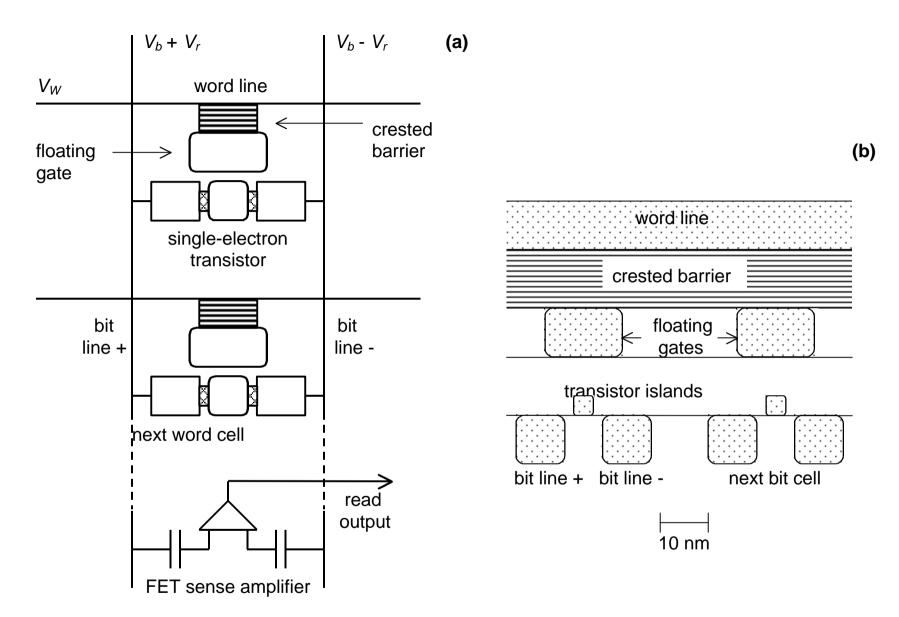

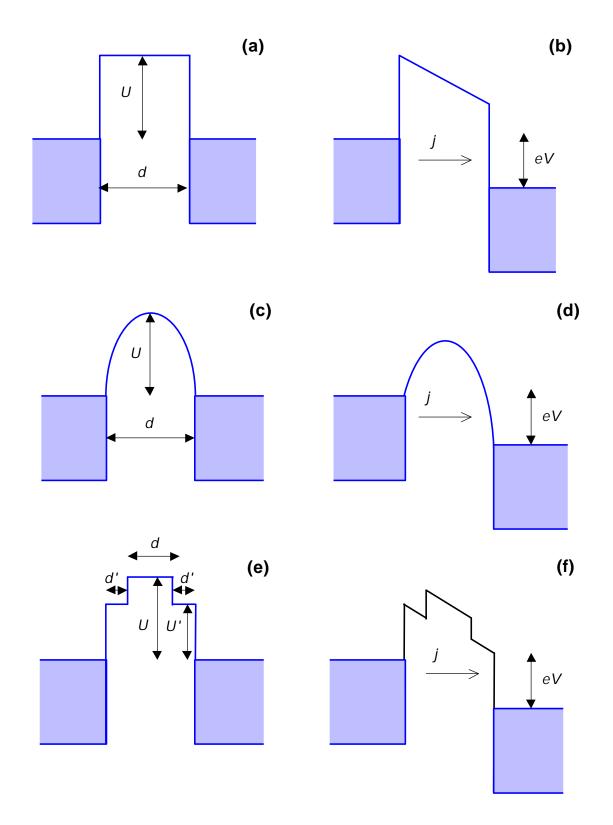

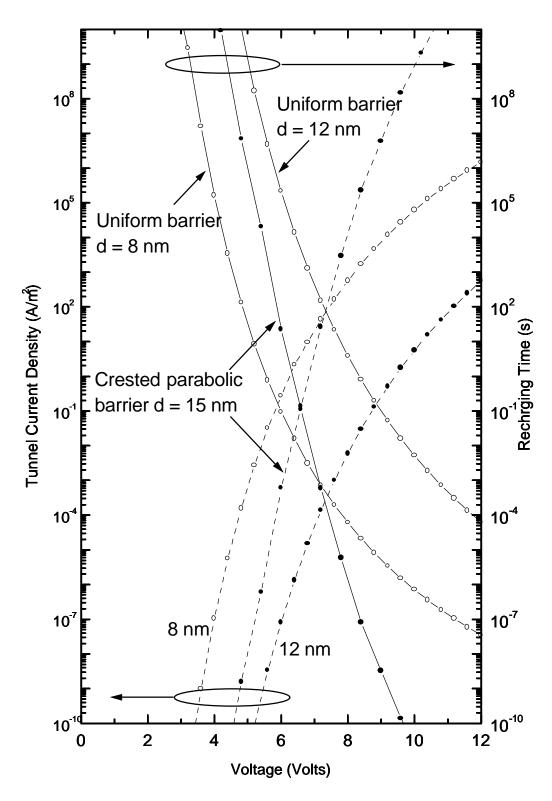

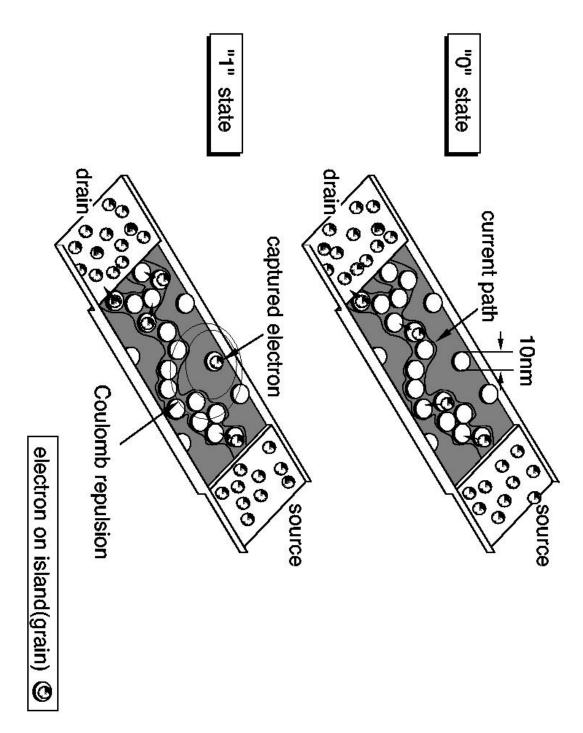

The memory concept suggested in Ref. 164 (Fig. 14) allows both these problems to be circumvented. A digital bit is stored in a relatively large conducting island (floating gate) in the form of 10 to 20 extra electrons which may be injected through a tunnel barrier using the Fowler-Nordheim process. During this WRITE process the injected electrons ramp up the electric potential U of the floating gate, so that the external charge  $Q_e$  of the single-electron transistor is ramped up

by *n'e*, with *n'*<*n* (*n'*~3). This ramp up causes *n'* oscillations of the transistor current (Fig. 6c). These oscillations are picked up, amplified, and rectified by a sense amplifier (one MOSFET seems sufficient for this purpose), the resulting signal  $V_{out}$  serves as the output. The main idea of this proposal is that the random background charge will cause only an unpredictable shift of the initial phase of the current oscillations, which does not affect the rectified signal. This concept has been verified in recent experiments [165] with a low-temperature prototype of the memory cell.

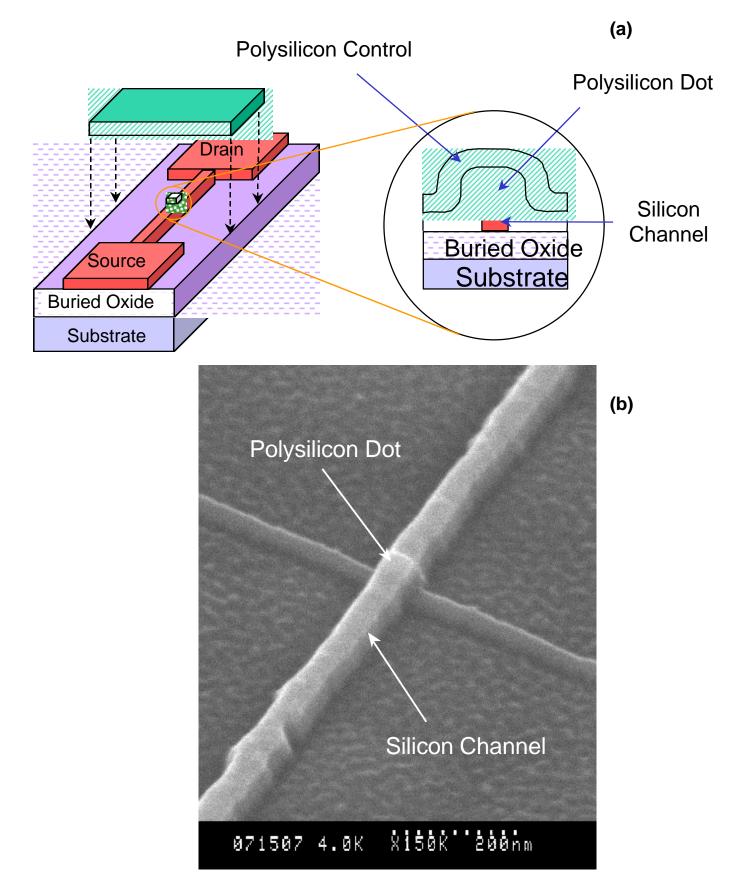

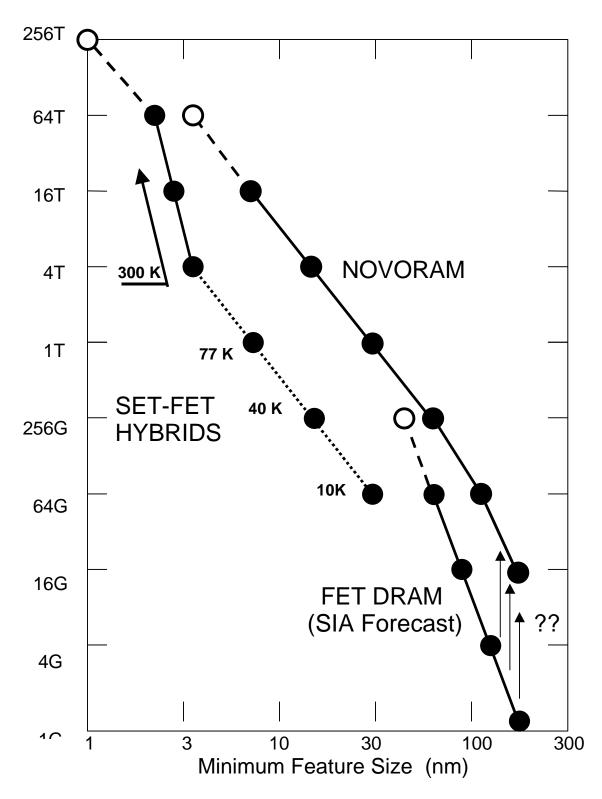

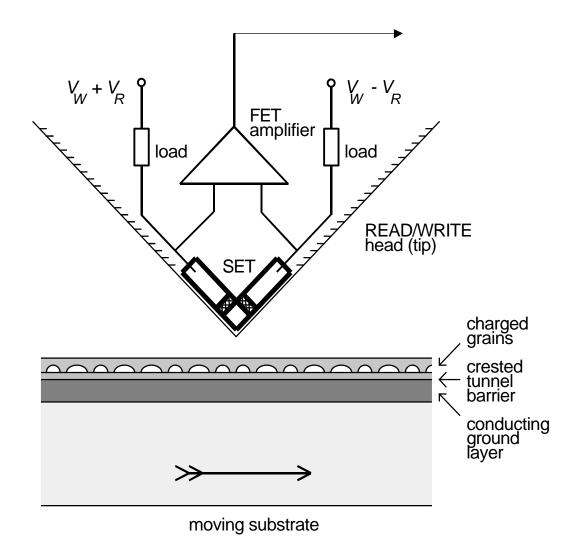

Notice that the readout in this memory is destructive: READ 0 is combined with WRITE 1 (the absence of output signal during WRITE 0 is achieved by turning off the source-drain voltage V), and requires the subsequent restoration of the initial contents of the cell. This operation, however, is not much more complex than refresh in an ordinary DRAM. The second relatively minor drawback is the need for a sense amplifier/rectifier. Estimates show that since the signals are pre-amplified with the single-electron transistor with its very low noise, one FET amplifier may serve up to 100 memory cells and hence the associated chip real estate per bit is minor. Figure 14b shows a possible layout of the memory cell for room temperature operation; even with due account of the sense amplifiers and drivers it is consistent with the very impressive  $10^{11}$  bit/cm<sup>2</sup> density. The estimated power density (~3 W/cm<sup>2</sup>, mostly in the sense amplifiers) also seems quite acceptable.