**Short Course 4**

### **Transient Measurements to Extract** Resistances and Material Properties with hands-on demonstrations

### Instructors:

András Poppe, PhD Gábor Farkas, PhD

Mentor Graphics Mechanical Analysis Division MicReD unit, Budapest, Hungary

# Basic concepts: $R_{th}$ , $Z_{th}$ , $\Psi$

### What thermal metric and why? R<sub>th</sub>

- A semiconductor device package can be well characterized for <u>steady-state operation</u> by its *thermal resistance*

- The thermal resistance is a number which tells us how many degrees of junction temperature elevation is caused if a unit dissipation applied to the device

- Power packages have large, exposed cooling tabs supporting heatsunk thermal management solutions: thermal resistance as a metric is not problematic

- There is a major, dominant heat-flow path from the junction to this cooling surface, resulting in an essentially 1D heat-flow

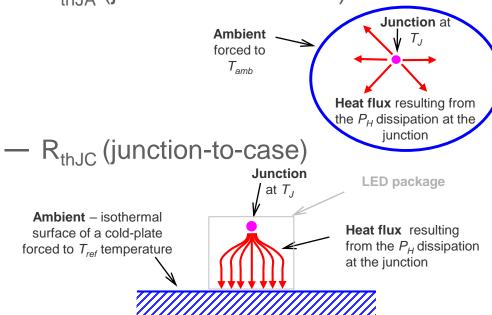

- The *junction-to-case* thermal resistance ( $R_{thJC}$  or  $\Theta_{JC}$ ) is a usual characteristic of such packages

- Thermal resistance is a thermal metric used

- To characterize "goodness" of a package

- Should allow fair comparison between different vendors' products

- Support simple system level thermal design

- Can be measured by simple tools as well as can be derived from transient measurements

### What thermal metric and why? Z<sub>th</sub>

- For the **dynamic properties**, the **thermal impedance** is the right characteristic:

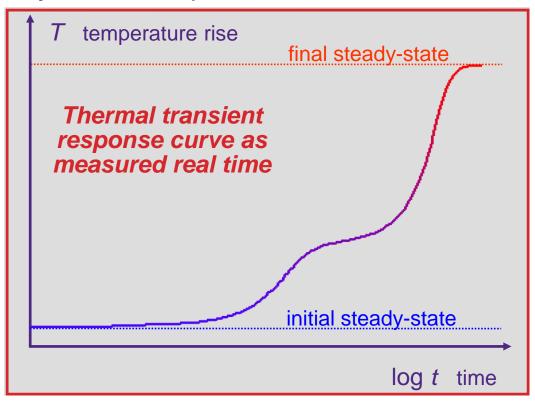

- The usual representation of the thermal impedance is the junction temperature transient obtained a response to a unit-height power step at the junction

- The thermal impedance carries all information about the heat-flow path such as

- thermal capacitance/resistance distribution along the heat-flow path

- Through this structural analysis is possible such as detection die attach problems and/or delamination/degradation of other thermal interfaces

- effective thermal impedance in dynamic mode of device operation

- PWM dimmed DC LEDs, AC driven LEDs, switching mode circuits (IGBTs)

- The thermal impedance is a unique characteristic of a package but can be represented in different forms

- Conventional Z<sub>th</sub>(t) diagrams

- Structure functions

- Dynamic (transient) compact thermal network models

- Complex locus in frequency domain

- Pulsed thermal resistance diagrams

- Thermal resistance is derived from thermal impedance; both require the amount of physical measurement time

### **Definition of thermal resistance?**

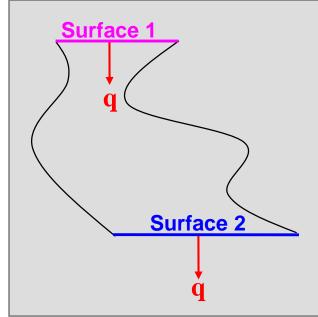

Required conditions to be able to define R<sub>th</sub> between two points in space:

1. surfaces must be isothermal

2. the entire heat-flux q entering the heat-flow path at Surface 1 must

leave at Surface 2

Real life situations: the above conditions are well met:

R<sub>th,JA</sub> (junction-to-ambient)

Same conditions apply also for *driving point* thermal impedances...

### A few words about thermal resistance

Original definition in the JEDEC JESD51-1 document

EIA/JEDEC Standard No. 51-1 Page 3

### 2. MEASUREMENT BASICS

The thermal resistance of a semiconductor device is generally defined as:

$$R_{JX} = \frac{TJ - Tx}{PH}$$

where  $R_{\theta JX}$  = thermal resistance from device junction to the specific environment (alternative symbol is  $\theta_{JX}$ ) [°C/W]

$T_J$  = device junction temperature in the steady state test condition [°C]

T<sub>X</sub> = reference temperature for the specific environment [°C]

P<sub>H</sub> = power dissipated in the device [W]

- Classically, for Si semiconductor diodes:  $R_{th} = \Delta T_J / (I_F \times V_F)$  (1a)

- For LEDs, consider the radiant flux:  $R_{th-r} = \Delta T_J / (I_F \times V_F P_{opt})$  (1b)

### Junction temperature — performance indicator

- Calculation:  $T_J = R_{th,J-X} \cdot P_H + T_X$ (2)

- R<sub>th,J-X</sub> junction-to-reference\_X <u>thermal resistance</u> supplied by the LED vendor

- P<sub>H</sub> <u>heating power</u> measured/calculated by the user

- $T_X$  <u>reference temperature</u> (un)specified by the LED user

- Used in the design process to decide if the foreseen cooling is sufficient or not...

- in case of LEDs, prediction of "hot lumens" is also required

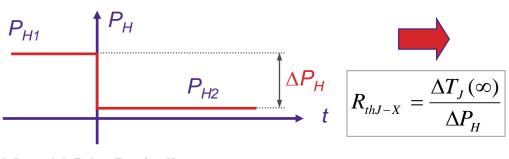

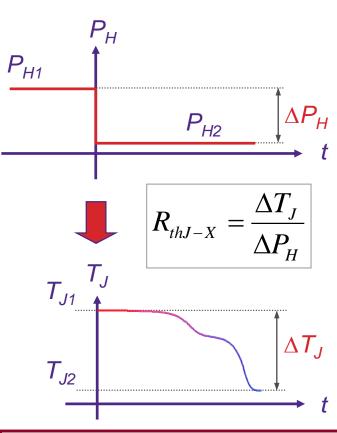

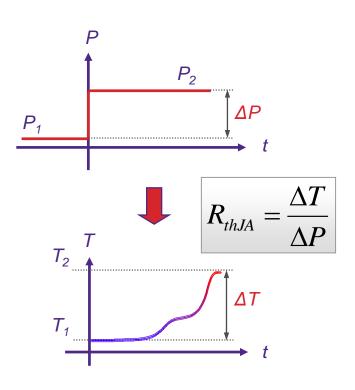

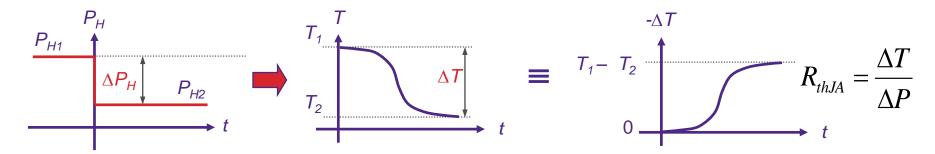

### Differential formulation of the thermal resistance

$$R_{thJ-X} = \frac{T_J - T_X}{P_H} = \frac{\left[\Delta T_J\right]_X}{P_H}$$

Instead of spatial difference (temperature values at  $R_{thJ-X} = \frac{I_J - I_X}{P_{tt}} = \frac{[\Delta I_J]_X}{P_{tt}}$  instead of spatial difference (temperature values at junction and reference point) temporal difference of the junction temperature can be used

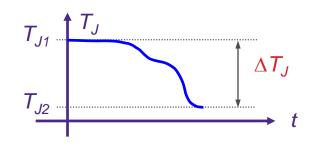

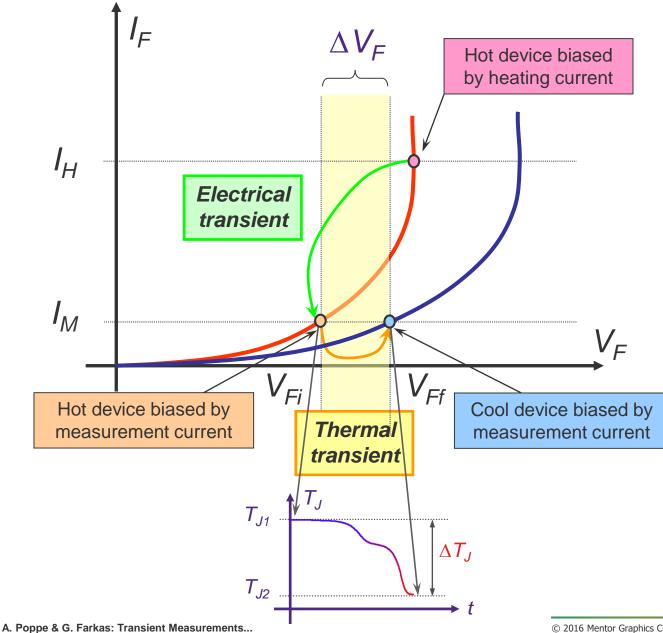

### Differential formulation of the thermal resistance

Alternate formulation: instead of spatial difference, we can also calculate with a <u>temporal difference</u> of the junction temperature (temp. transient):

$$R_{th\ J-X}(t) = \Delta T_J(t) / \Delta P_H$$

is called **Z**<sub>th</sub> **curve**

$$T_{J1} = R_{th\ J-X} \cdot P_{H1} + T_X \tag{4a}$$

$$T_{J2} = R_{th\ J-X} \cdot P_{H2} + T_X \tag{4b}$$

$$T_{J2} - T_{J1} = R_{th \ J-X} \cdot (P_{H2} - P_{H1})$$

(5)

Let  $T_{J1}=T_J(t_1)$  and  $T_{J2}=T_J(t_2)$ :

$$R_{th J-X} = [T_J(t_2) - T_J(t_1)] / (P_{H2} - P_{H1})$$

(6)

$$R_{th J-X}(t) = \Delta T_{J}(t) / \Delta P_{H}$$

(7)

If

$$t_1$$

=0 and  $t_2$ = $\infty$   $\Rightarrow$   $R_{th \ J-X}$ = $\Delta T / \Delta P_H$

If

$$P_{H2} = 0$$

, then  $T_{J2} = T_X$

### The JEDEC thermal testing standards

### Why to use standards?

- Our goals by using standards is to make sure that what we do is

- Commonly understood by others

- → standards are publicly available by anybody

- Is repeatable by others

- → standards can be implemented by anybody

- Is compatible with what others do

- → if most vendors / end-users apply the same standards, results can be compared

- Measurement standards

- Provide definitions of terms/quantities/metrics

- Define test methods and procedures

- Define test environments

- Define data reporting

- Standard thermal tests reflect characteristics of test devices and conditions, not real-life applications

- One has inherently to simplify conditions compared to real-life, otherwise the goals (common understanding & reproducibility) can not be guaranteed

### Standards make measurements reproducible

- Real life conditions must be simplified for standardized measurements

- Good standards provide metrics which are close to real life conditions

- Deviation from real-life conditions must be on the "safe" side

- Example for simplification of real life conditions

- Real life horse

Too many individual, particular details

- color

- sex, muscles, teeth, etc

"Standard" horse

No individual details, but major characteristics of a real horse maintained

- has got four legs,

- has got a body, a neck, a head and a tail

- weight and form factor close to an average horse

Original standard horse example from Bruce Guenin, chairman of the JEDEC JC15 Committee on standardization of thermal characterization of packaged semiconductor devices

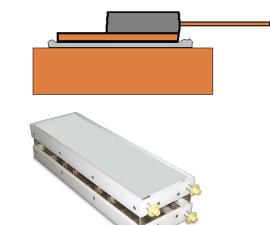

### Example from electronics cooling: power transistor

How test conditions of power transistors can be standardized?

Real life horse

"Standard" horse

Implementation of the "Standard" horse

Standard features Additional features

Real life application environment of **power transistors**: attached to a forced air cooled heat-sink

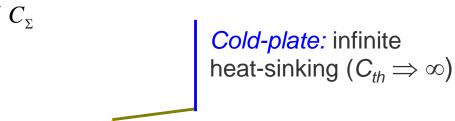

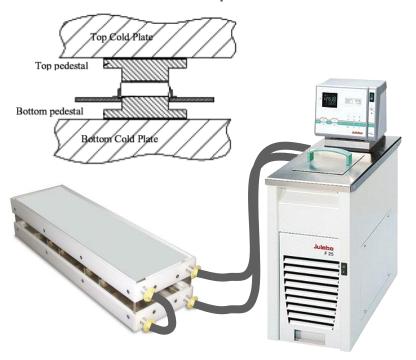

Standard test condition of **power transistors**: attached to a liquid cooled cold plate

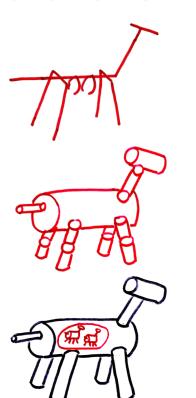

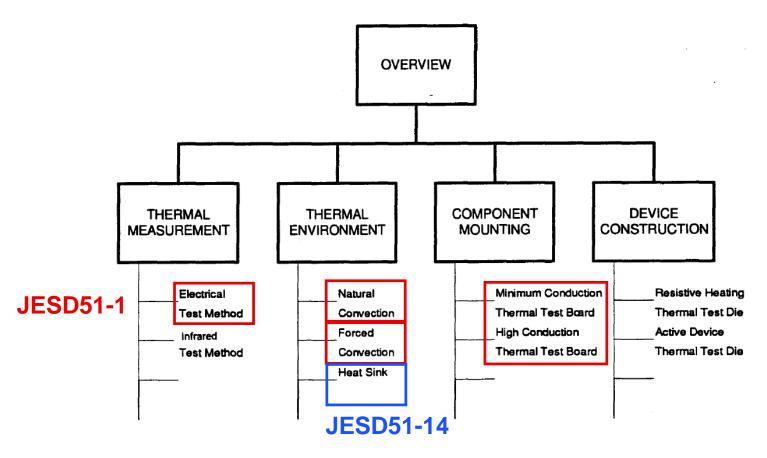

### JEDEC thermal characterization standards

Classical standards: JESD51- series of documents

"JEDEC standard" horse

"JEDEC standard STATIC horse": JESD51-\* series (1,2,3,4, etc) provide

- terms and definitions

- basic test methods (electrical test methods: static / dynamic)

- test environments (natural convection, forced air) and test boards

- data reporting guidelines

JESD51 overview document

- Some "new" JEDEC thermal standards:

"JEDEC standard horse models": JESD15-\* series for thermal compact modeling of packages

- compact modeling overview

- 2R and DELPHI models

Work on standard model library file format in progress

"JEDEC standard DYNAMIC horse": JESD51-14 – the first thermal transient testing standard using structure functions

- new standard for junction-to-case thermal resistance measurement

- defines a cold plate as test environment

- defines thermal transient measurement and structure function analysis as test method

**Extension of** JESD51-\* series standards to account for multi-chip packages

• JESD51-3x documents extend definitions of environmental conditions and test boards for multi-die packages

### List of JEDEC thermal characterization standards

Below we give the comprehensive list of JEDEC thermal measurement and modeling standards:

### Classical set of standards for steady-state measurements:

- JESD51 Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device) (1995)

- JESD51-1 Integrated Circuits Thermal Measurement Method Electrical Test Method (Single Semiconductor Device) (1995)

- JESD51-2A Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection (Still Air) (2008)

- JESD51-3 Low Effective Thermal Conductivity *Test Board* for Leaded Surface Mount Packages (1996)

- JESD51-4 Thermal Test Chip Guideline (Wire Bond Type Chip) (1997)

- JESD51-5 Extension of Thermal *Test Board* Standards for Packages with Direct Thermal Attachment Mechanisms (1999)

- JESD51-6 Integrated Circuit Thermal Test Method Environmental Conditions Forced Convection (Moving Air) (1999)

- JESD51-7 High Effective Thermal Conductivity *Test Board* for Leaded Surface Mount Packages (1999)

- JESD51-8 Integrated Circuit Thermal Test Method Environmental Conditions Junction-to-Board (1999)

- JESD51-9 Test Boards for Area Array Surface Mount Package Thermal Measurements (2000)

- JESD51-10 Test Boards for Through-Hole Perimeter Leaded Package Thermal Measurements (2000)

- JESD51-11 Test Boards for Through-Hole Area Array Leaded Package Thermal Measurements (2001)

- JESD51-12 Guidelines for Reporting and Using Electronic Package Thermal Information (2005)

- JESD51-13 Glossary of Thermal Measurement Terms and Definitions (2009)

### The first transient measurement standard:

JESD51-14 Transient Dual Interface Test Method for the Measurement of the Thermal Resistance Junction to Case of Semiconductor Devices with Heat Flow Trough a Single Path (2010)

### LED thermal testing standards:

JESD51-5x Anew subgroup of thermal testing standards aimed at power LEDs (2012)

### Extension of existing standards to multi-chip packages:

- JESD51-31 Thermal Test Environment Modifications for Multi-Chip Packages (2008)

- JESD51-32 Extension to JESD51 Thermal Test Board Standards to Accomodate Multi-Chip Packages (2010)

### Compact modeling guidelines:

- JESD15-1 Compact Thermal Model Overview (2008)

- JESD15-2 Terms and Definitions for Modeling Standards (not yet launched)

- JESD15-3 Two-Resistor Compact Thermal Model Guideline (2008)

- JESD15-4 DELPHI Compact Thermal Model Guideline (2008)

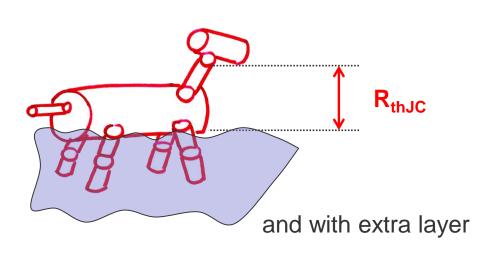

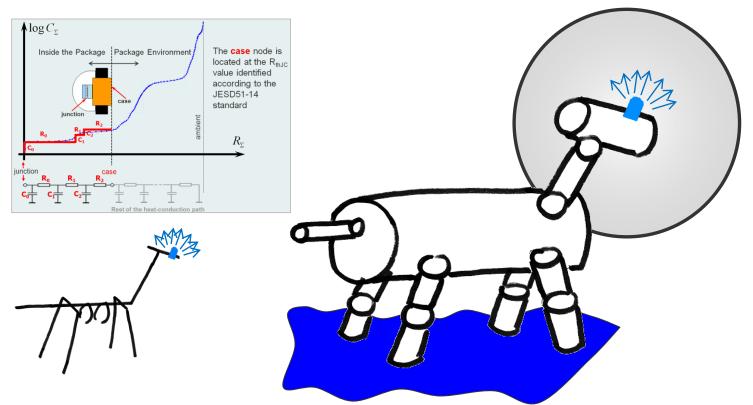

### New standard "horses" – R<sub>thJC</sub> with transient (2010)

■ JESD51-14: R<sub>thJC</sub> measurement with the dual thermal interface method

Measure twice: without

- Location of deviation with respect to the junction defines R<sub>thJC</sub>

- Published in November 2010

- Applicable to power semiconductor device packages with an exposed cooling surface and a single heat-flow path

- This condition is valid power LEDs as well, thus

- JESD51-14 well applicable to LEDs provided that, ....

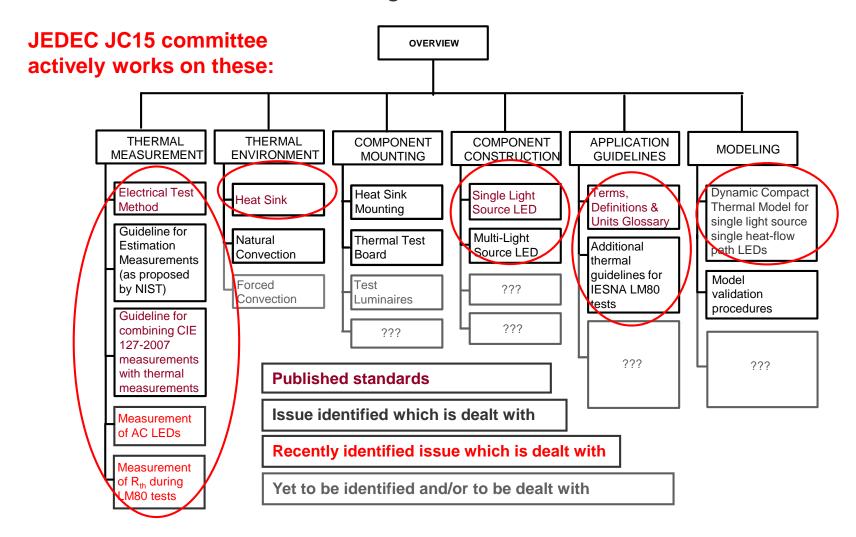

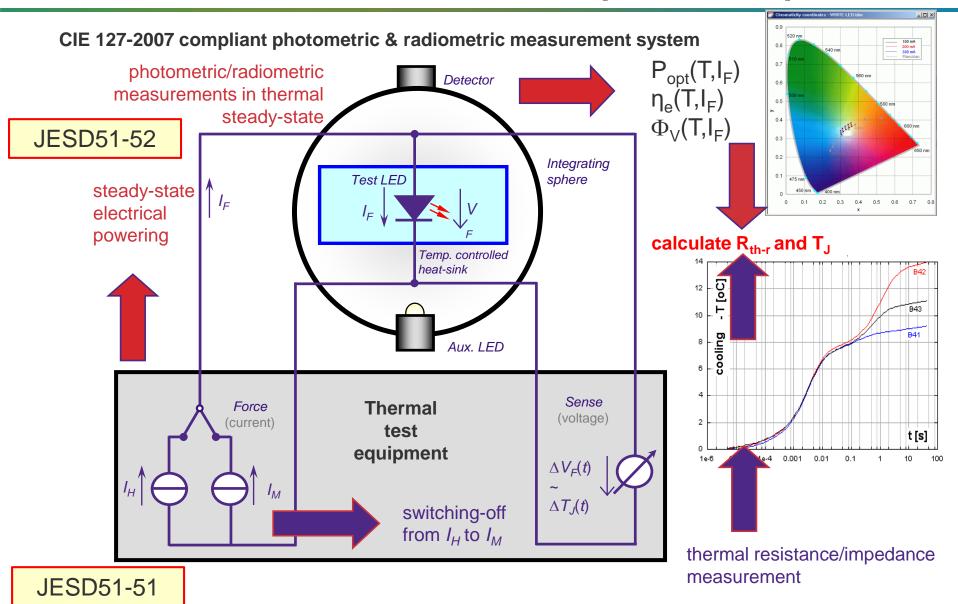

### New standard "horses" – LED testing (2012)

JESD51-50, 51, 52, 53 series LED thermal testing guidelines

Measure the emitted light as well to account for the actual heating Measure on cold-plate to assure thermal steady-state for light measurements

This combined with a JESD51-14 compliant R<sub>thJC</sub> measurement allows test based compact thermal modeling of power LED packages

Will be discussed later today...

### **Approach of the JEDEC JC15 committee**

JESD51-50: LED thermal testing overview document

### Standards are downloadable from www.jedec.org:

14 March 2016

### The JESD51 standard — overview document

The thermal testing standards follow a modular structure:

Each group will have one or more applicable documents to reflect different thermal measurement requirements. Because environmental conditions, component mounting approaches and device construction techniques and processes will change as technology changes, additional documents will be added to these groups as the needs arise and standards established. As appropriate, each of

### The JESD51-1 electrical test method

- Direct measurement of a single temperature: average temperature, good time resolution

- Electrical test method to measure junction temperature:

- Temperature measured by the change of a temperature sensitive parameter of the semiconductor (TSP) device (e.g. diode forward voltage, MOSFET threshold voltage)

- Measures the junction temperature through an electrical signal of the TSP

- Needs calibration

- Two test methods: static and dynamic test method

- Thermocouples

- Large, error due to alternate heat-flow via the thermocouple itself

- Used typically to measure / monitor environmental conditions

- Thermal transient measurements are based on the electrical test method

- smart implementation of the JESD51-1 static test method

- completed with structure function analysis adds extra value:

insight into the details of the heat-flow path

### A few words about the thermal resistance

### Original definition in the JEDEC JESD51-1 document

EIA/JEDEC Standard No. 51-1 Page 3

### 2. MEASUREMENT BASICS

The thermal resistance of a semiconductor device is generally defined as:

$$R_{JX} = \frac{TJ - Tx}{PH} \tag{1}$$

where  $R_{\theta JX}$  = thermal resistance from device junction to the specific environment (alternative symbol is  $\theta_{JX}$ ) [°C/W]

T<sub>J</sub> = device junction temperature in the steady state test condition [°C]

T<sub>X</sub> = reference temperature for the specific environment [°C]

P<sub>H</sub> = power dissipated in the device [W]

The device junction temperature in the test condition can be determined by:

$$T_J = T_{J0} + \Delta T_J \tag{2}$$

where T<sub>J0</sub> = initial device junction temperature before heater power is applied [°C]

ΔT<sub>J</sub> = change in junction temperature due to heater power application [°C]

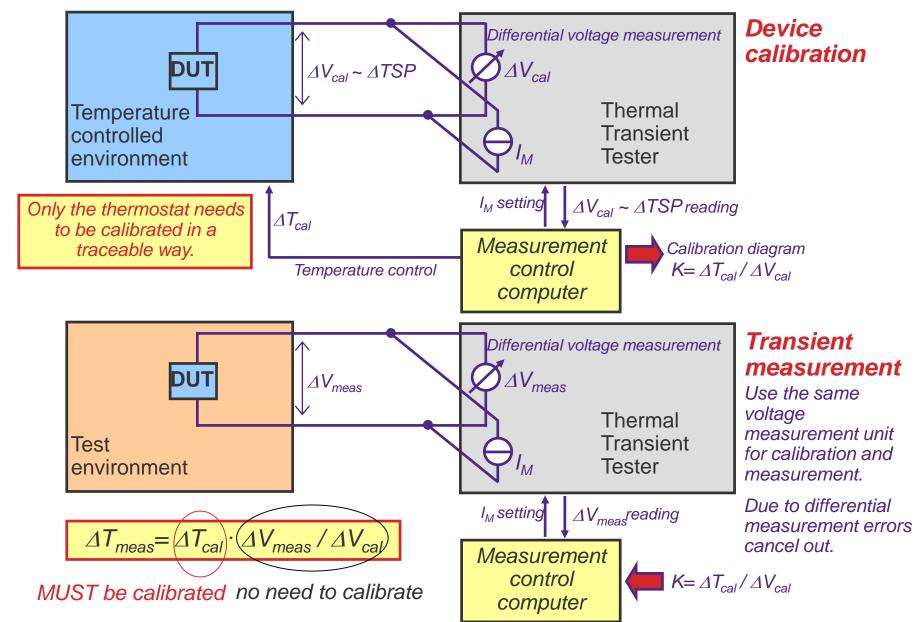

The Electrical Test Method (ETM), described herein, makes use of a temperature-sensitive parameter (TSP) to sense the change in temperature of the junction operating area due to the application of electrical power to the device-under-test (DUT). In equation terms,

$$\Delta T_{J} = K \times \Delta T S P \tag{3}$$

where  $\Delta TSP$  = change in temperature-sensitive parameter value [mV] K = constant defining relationship between changes in  $T_J$  and TSP [°C/mV]

21

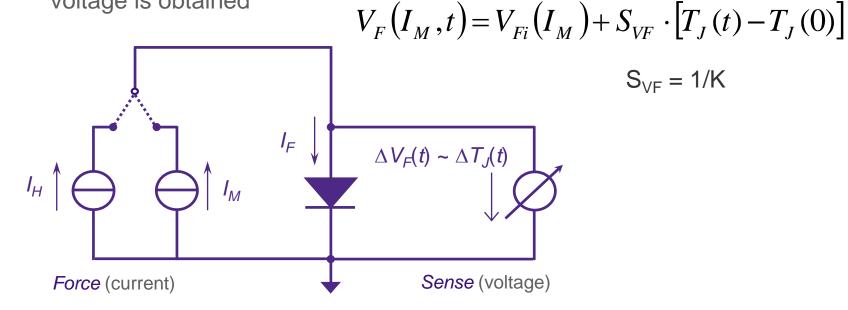

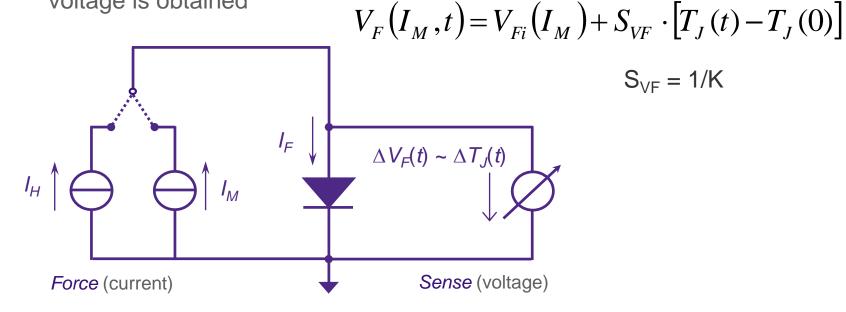

### How do we know $\Delta T_i(t)$ ?

- PN junctions' forward voltage under forced current condition can be used as a very accurate thermometer

- The change of the forward voltage (TSP temperature sensitive parameter) should be carefully calibrated against the change of the temperature (see JEDEC JESD51-1 and MIL-STD-750D)

— In the calibration process the  $S_{VF}$  temperature sensitivity of the forward voltage is obtained

$S_{VF} = 1/K$

Forward voltage change due to temperature change is measured using a 4 wire setup (Kelvin setup)

### The static test method

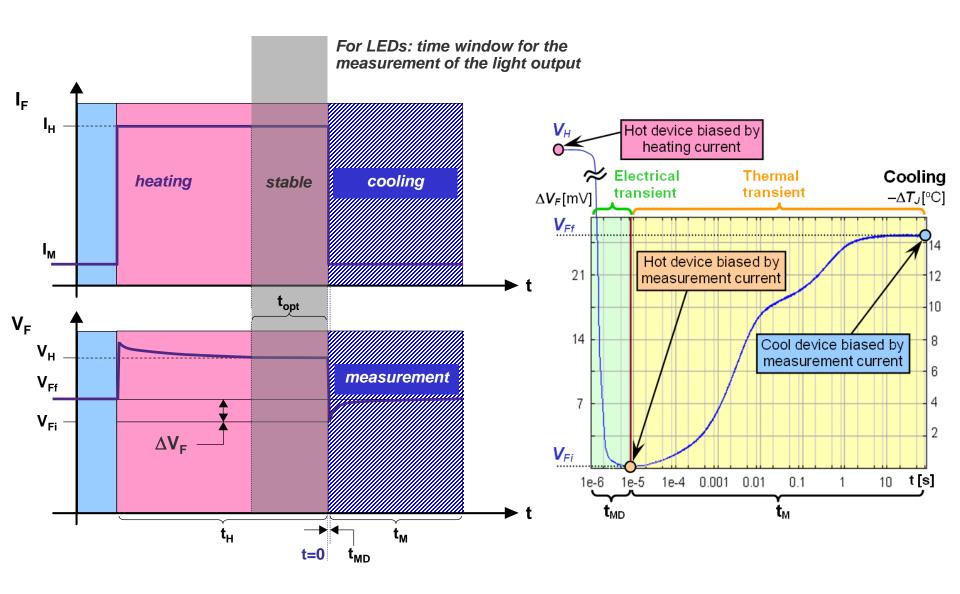

- According to the JESD51-1 document two test methods are defined: dynamic test method and static test method

- Static test method or continuous measurement.

- Switch on heating at the junction

- Wait for the steady state be reached (when junction is hot)

- Measure the junction temperature and identify the heating power

- Switch off the heating

- Wait for the steady state be reached (when junction is cool)

- Measure the junction temperature

### Assumption of the standard:

- At cold steady-state 0 power is applied → junction temperature is equal to the temperature of the ambient (reference environment)

As we shall see, this assumption is not really needed

- Extension of the basic static test method: real transients

- Measure the actual change of the junction temperature after the power is switched off (or on) continuously, resulting in a real junction temperature transient

- Completely differential approach in which switching off or on the power is symmetrical

- Measurement is followed by mathematical post processing resulting in structure functions and other descriptive functions

### The principle of the extended static test method

Due to switching the power, temperature changes:

Switch the power on (or off) in steady state and wait for the other steady state to occur.

While waiting for reaching the other steady-state, **measure** (record) the real transient continuously, as it takes place.

### Measurement of $\Delta T_J(t)$ continuously "on-the-fly":

- This test method is less problematic: the JESD51-1 document does not prescribe detailed procedures to avoid problems

- In the static test method only one switching takes place:

- switch ON the power: capture a heating transient continuously

- switch OFF the power: capture a cooling transient continuously

- After changing the heating power in a step-wise manner no further switching takes place

- no problems related to  $t_{MD}$  selection no measurement delay is needed

### 2.2 COOLING TIME CONSIDERATIONS

### JESD51-1 document

<u>COOLING TIME considerations are NOT applicable to the Static Mode of testing</u> because the monitoring of the temperature-sensitive parameter occurs on a continuous basis while the heating power is applied to the DUT.

— the only concern is the possible electrical transient at t=0+

### Essentials of the JESD51-1 electrical test method

### How do we know $\Delta T_i(t)$ ?

- PN junctions' forward voltage under forced current condition can be used as a very accurate thermometer

- The change of the forward voltage (TSP temperature sensitive parameter) should be carefully calibrated against the change of the temperature (see JEDEC JESD51-1 and MIL-STD-750D)

— In the calibration process the  $S_{VF}$  temperature sensitivity of the forward voltage is obtained

$S_{VF} = 1/K$

Forward voltage change due to temperature change is measured using a 4 wire setup (Kelvin setup)

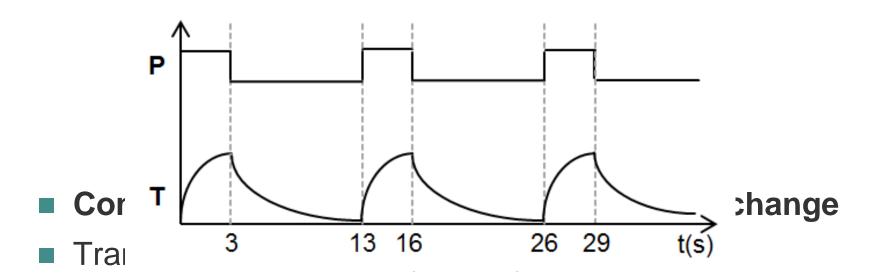

### The measurement waveforms

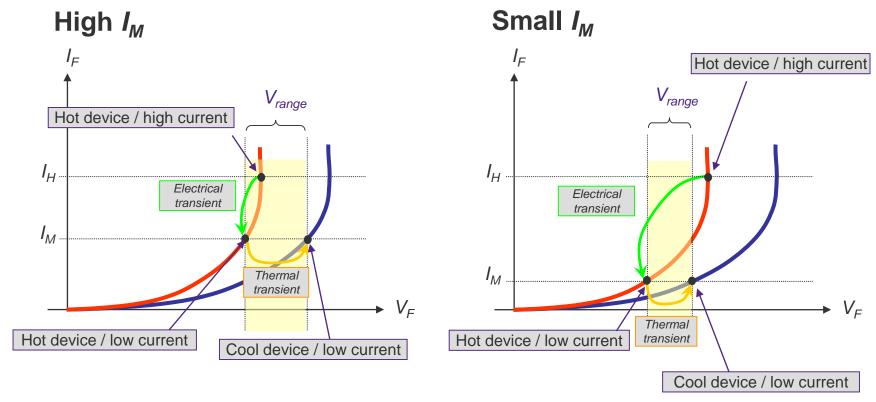

### The transient processes in the I-V characteristic:

14 March 2016

### Heating vs. cooling?

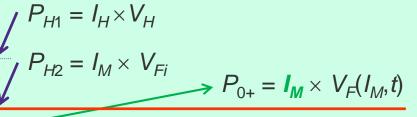

$$P_{-0} = I_H \times V_F(I_H, t)$$

Negligible error term:

$$I_{M} \ll I_{H}$$

### The power step at heating:

$$P_{0-}(t) = I_M \times V_F(I_M, t)$$

Error term calculation will follow later...

$$P_{0-} \longrightarrow P_{0+}(t) = I_{H} \times V_{F}(I_{H}, t)$$

Considerable error term:

$$I_H >> I_M$$

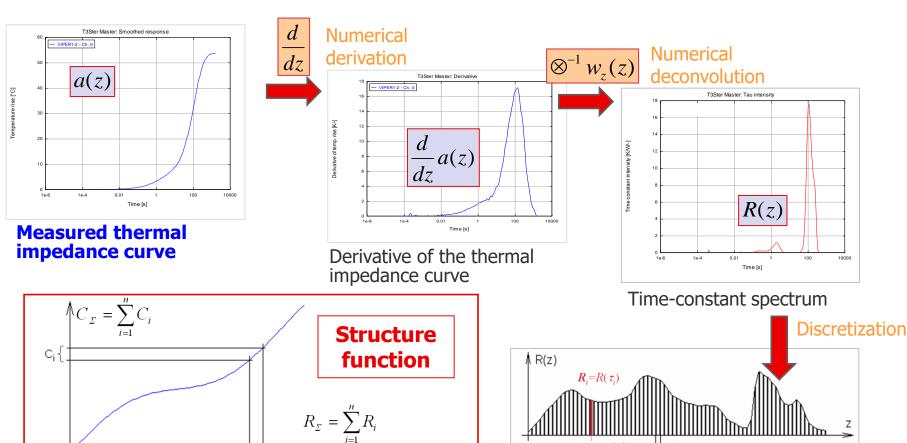

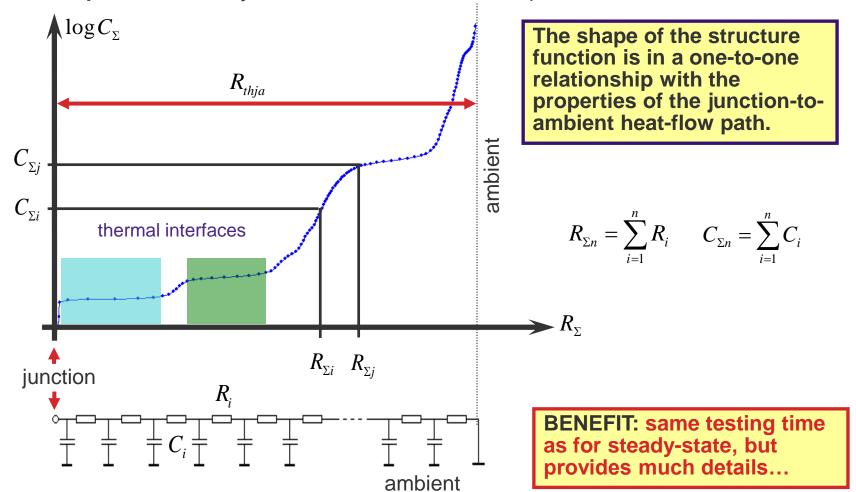

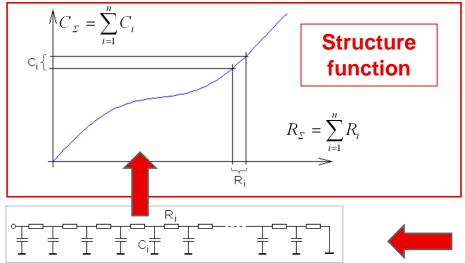

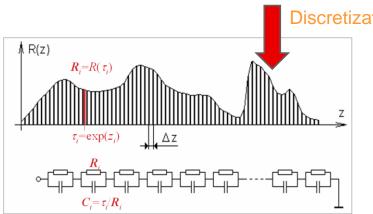

### Converting Z<sub>th</sub> curves to structure functions

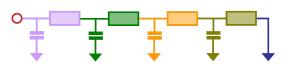

Foster model of the impedance

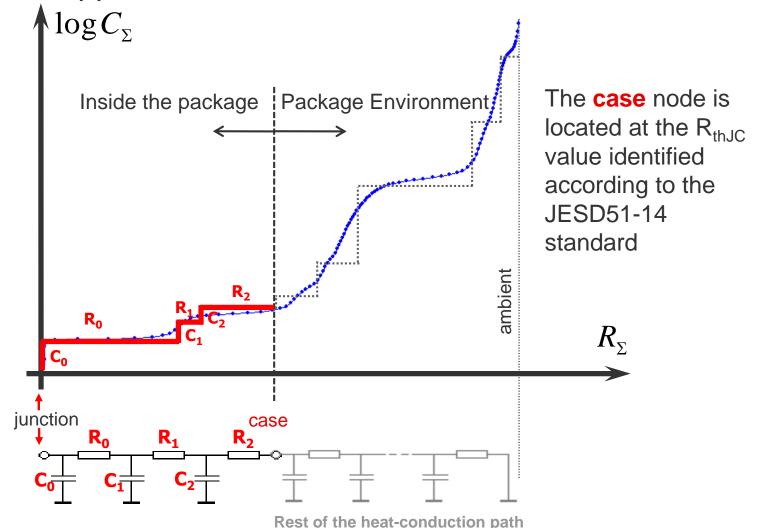

### The Structure Function

The *structure function* is the *graphical representation* of the *network model of the thermal impedance* of the junction-to-ambient heat-flow path.

The structure function illustrates the way how heat flows though a package.

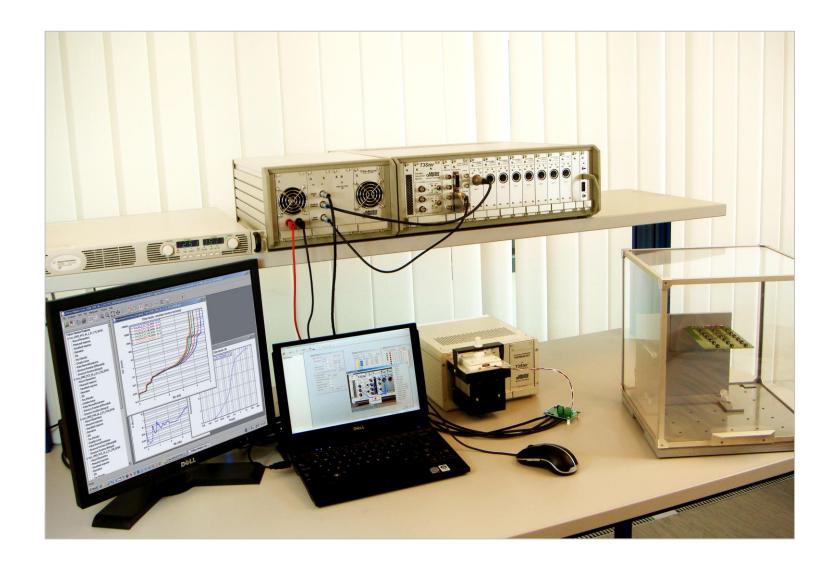

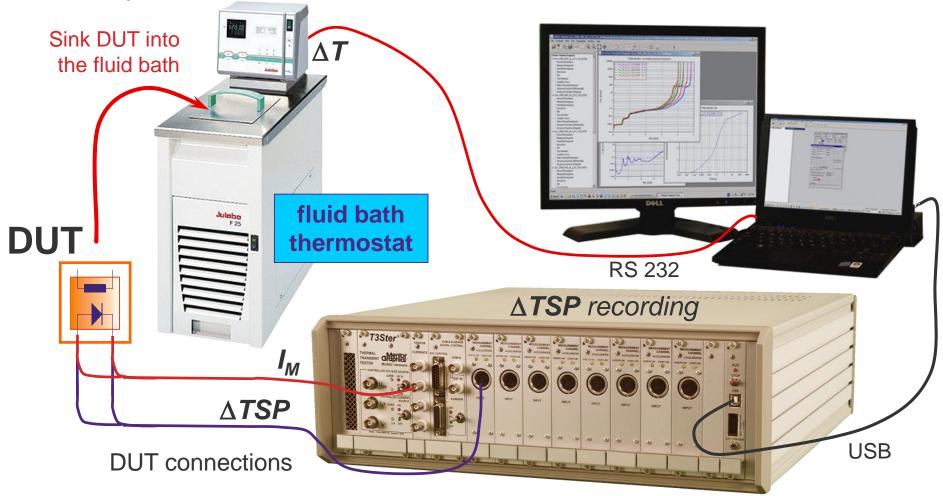

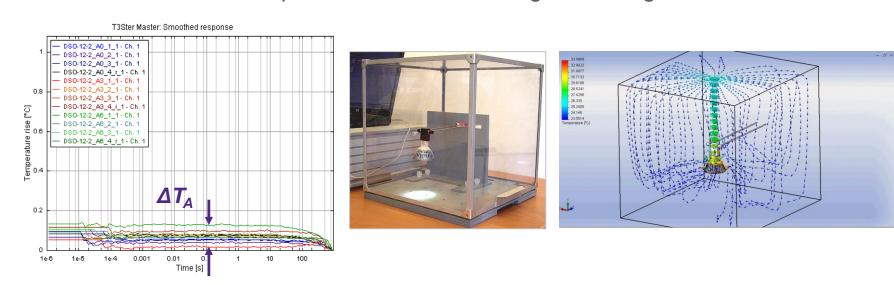

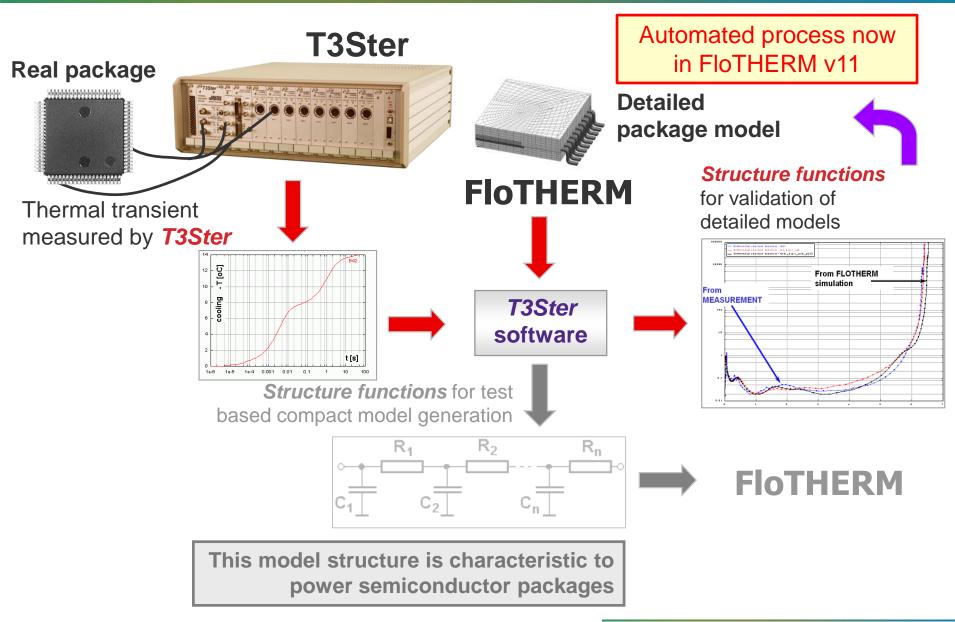

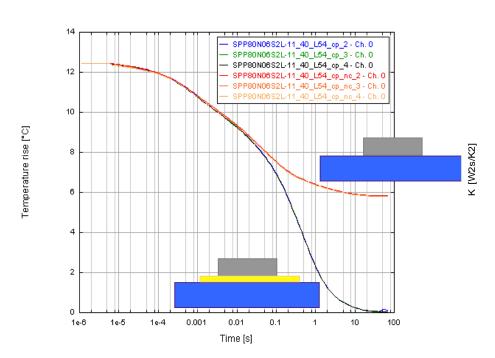

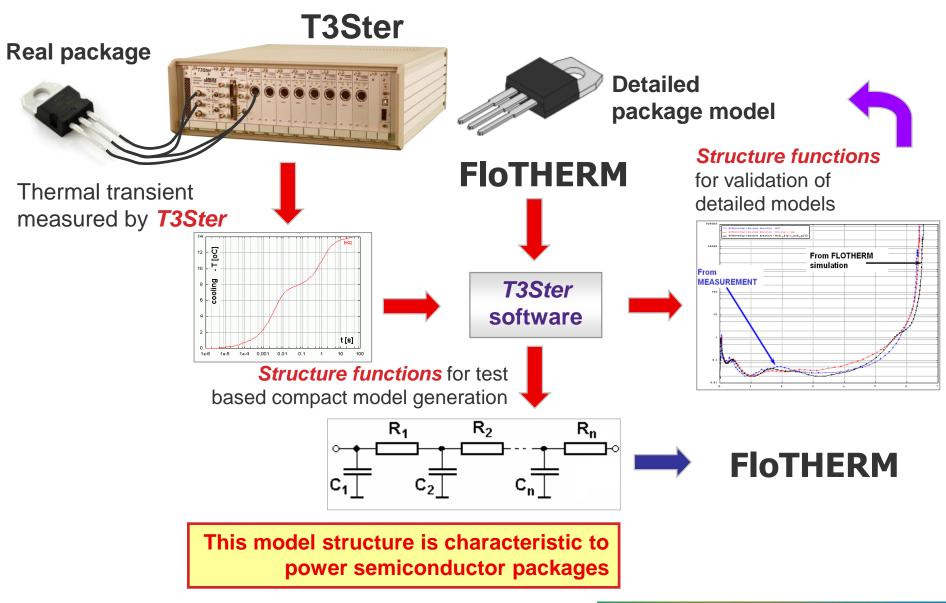

### Mentor Graphics MicReD implementation: T3Ster

- The JEDEC JESD51-1 static test method is implemented by the T3Ster equipment (thermal transient tester) and its measurement software

- real-time measurement of actual junction temperature transients either in heating mode or in cooling mode

- for diodes cooling mode is recommended (since higher accuracy available this way)

- for transistors, thermal test dies with separate heaters and sensors both heating and cooling modes are recommended

- K-factor calibration is provided

- Measured transients are post-processed by the T3Ster Master software, providing

- structure functions and

- other alternate representations of the measured thermal impedance such as

- complex loci

- time-constant spectra

- pulsed thermal resistance diagrams

- dynamic compact thermal network models

### Mentor Graphics MicReD implementation: T3Ster

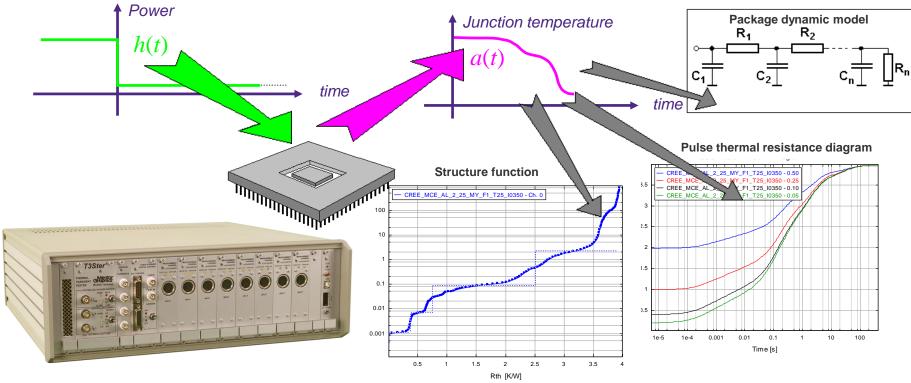

### Summary of thermal transient testing using T3Ster

- The h(t) step-wise change in heating is applied at the junction (abrupt switching)

- The a(t) temperature response at the junction is being measured (unit-step response function) while linearity is assumed

- All available information is extracted from a(t) using sophisticated mathematical procedures

- structure function, derivative of structure function

- compact dynamic thermal models

- pulsed thermal resistance / complex locus (frequency domain representation)

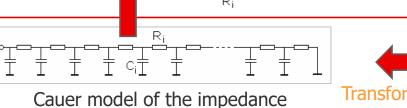

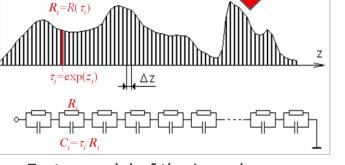

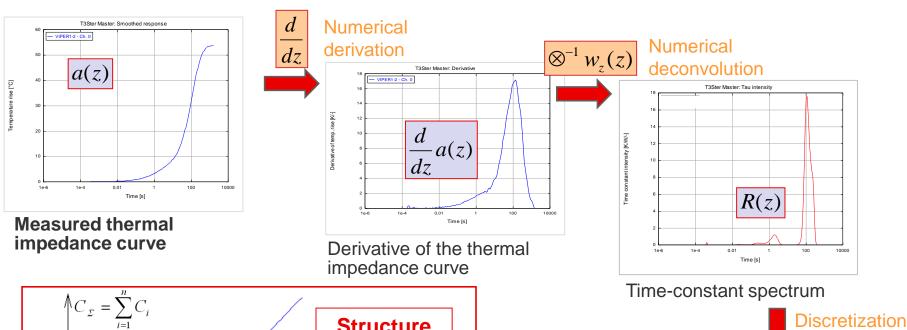

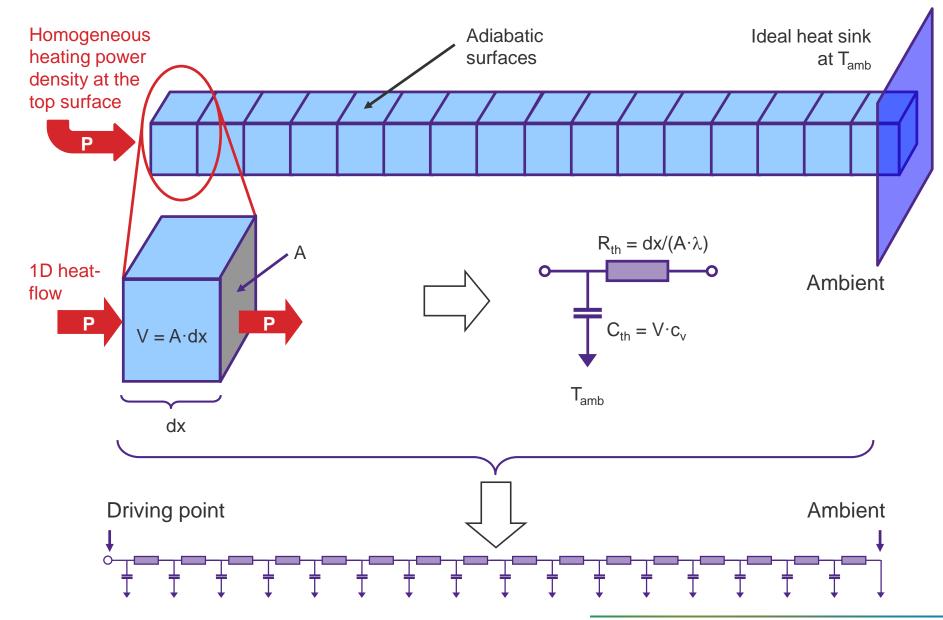

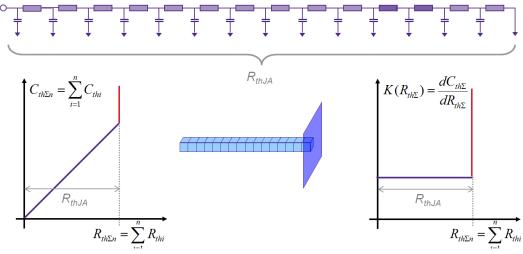

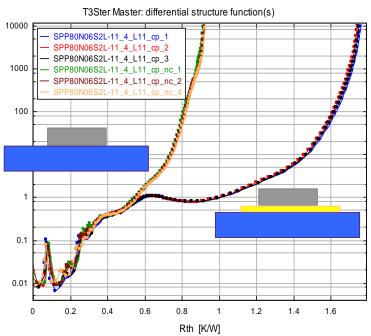

# The structure functions

### How Do We Get Them in the *T3Ster* software?

Foster model of the impedance

Cauer model of the impedance

Structure function

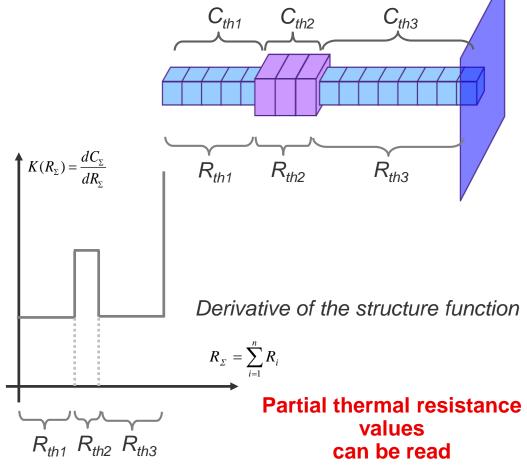

**Derivative of structure function**

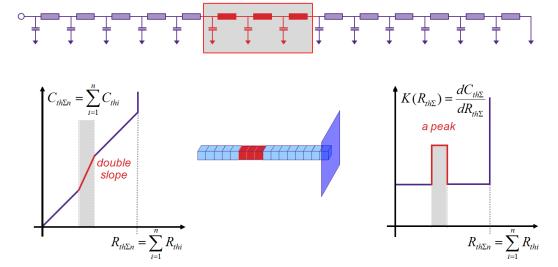

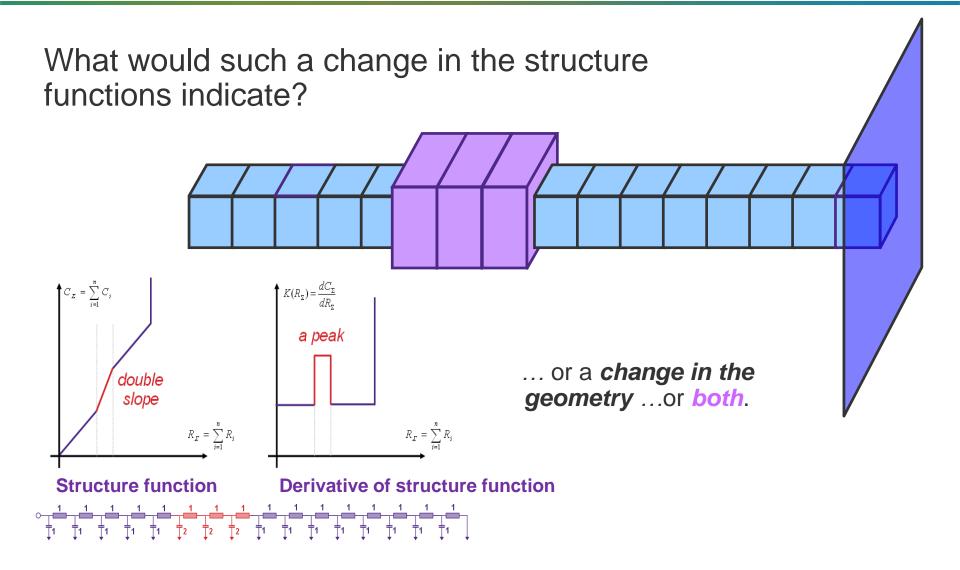

Structural or material property changes are clearly indicated both by the cumulative and the differential structure functions

**Structure function**

**Derivative of structure function**

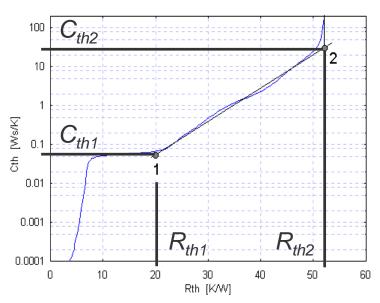

What would such a change in the structure functions indicate?  $C_{\mathcal{Z}} = \sum_{i=1}^{n} C_{i}$ a peak It means either a double change in the material slope properties... Structure function **Derivative of structure function**

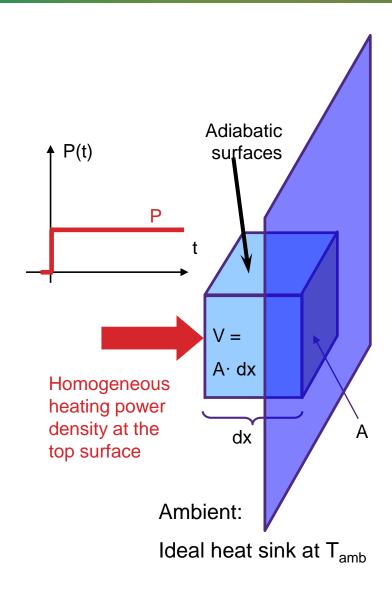

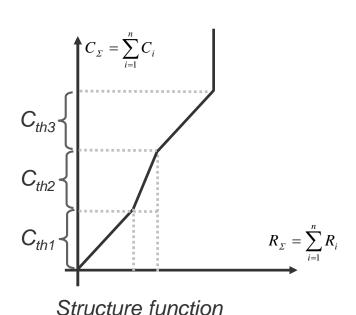

What values can we read from the structure functions?

Thermal capacitance values can be read

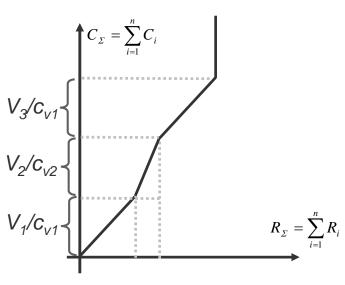

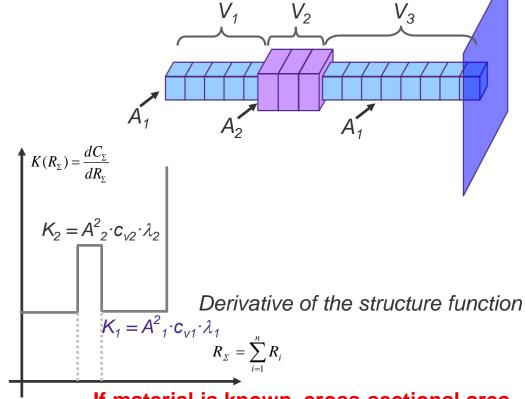

What values can we read from the structure functions?

Structure function

If material is known, volume can be identified.

If volume is known, volumetric thermal capacitance can be identified.

If material is known, cross-sectional area can be identified.

If cross-sectional area is known, material parameters  $(c_{\nu} \cdot \lambda)$  can be identified.

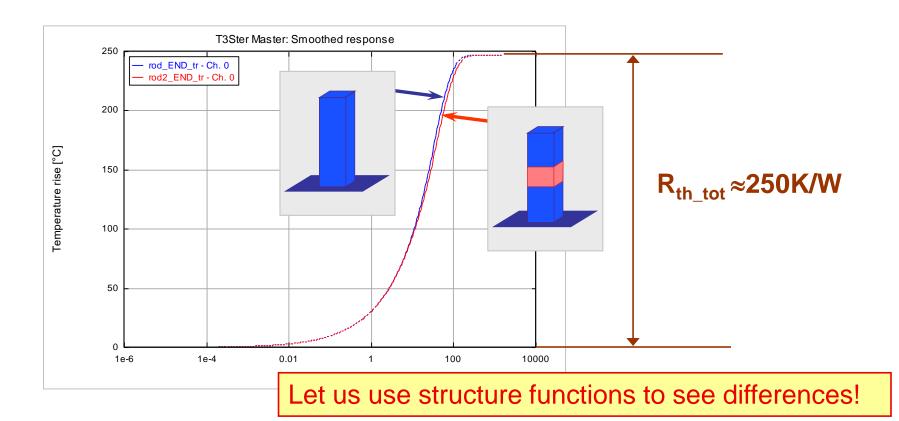

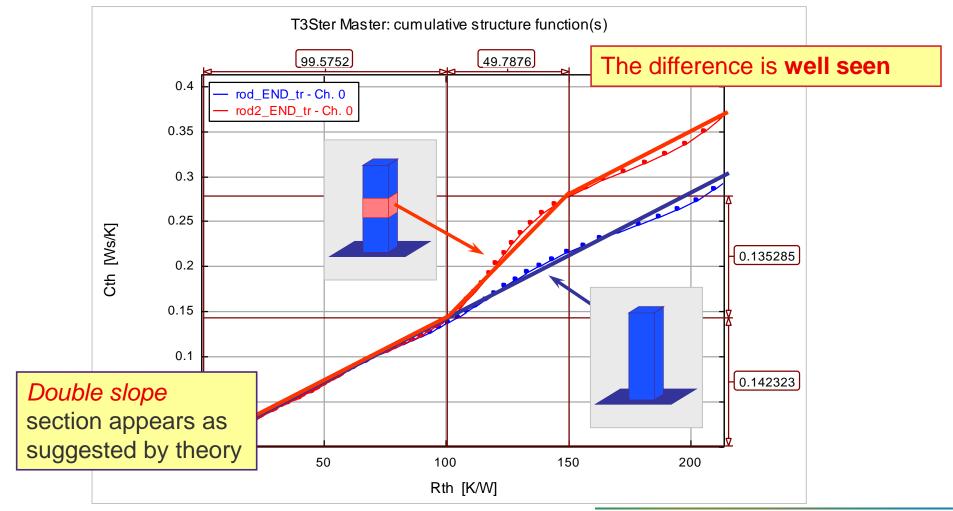

### Simulation Experiment for Rods

- A Cu rod of 1x1mm<sup>2</sup> cross-sectional area and 100mm length was simulated ( $\lambda$ =402 W/mK, C<sub>v</sub>=3.4e6W/m<sup>3</sup>K)  $\Rightarrow$  R<sub>th tot</sub>  $\approx$  250 K/W

- Change applied: 40mm normal Cu, 20mm with double C<sub>v</sub> value, 40mm normal Cu

### **Simulation Experiment for Rods**

The same results in structure functions:

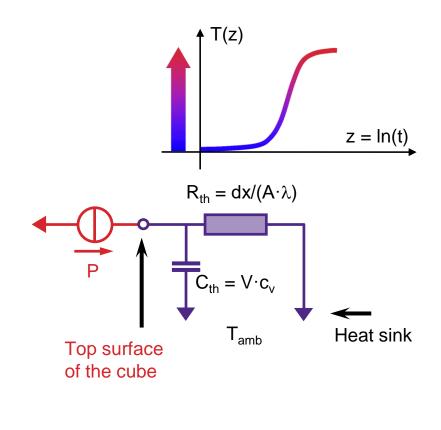

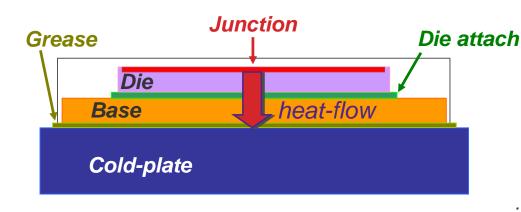

### Structural / network model of the heat-flow path

### **The Structure Function**

We measure the **thermal transient** at the junction...

...and we convert it into the **cumulative structure function and a <u>compact model</u>**:

Allows structural analysis and modeling...

Junction: is always in the origin

Grease: large  $R_{th}/C_{th}$  ratio Base: small  $R_{th}/C_{th}$  ratio

Die attach: large  $R_{th}/C_{th}$  ratio

Die: small  $R_{th}/C_{th}$  ratio

$R_{\Sigma}$

### **Application in QA (failure analysis)**

### **The Structure Function**

Reference device with good DA Unknown device with suspected DA voids **Junction Junction** Die attach Grease Grease Die attach Chip Chip Base Base Cold-plate Cold-plate Identify its structure Identify its structure function: function:  $C_{\Sigma}$  $C_{\scriptscriptstyle \Sigma}$ Copy the reference structure function into Grease this plot his difference is Base showing us a reliability problem Die attach Chip This increase  $R_{\Sigma}$ suggests DA voids

### **Features of Structure Functions**

- For certain types of 1D spreading, analytical formulae can be given

- For "ideal" cases structure functions can be given even by analytical formulae

- for a rod:  $C_{\Sigma} = const \cdot R_{\Sigma}$

- for radial spreading in a disc of w thickness and  $\lambda$  thermal conductivity:

$$\lambda w = \frac{1}{4\pi} \frac{\ln(C_{th2} / C_{th1})}{R_{th2} - R_{th1}}$$

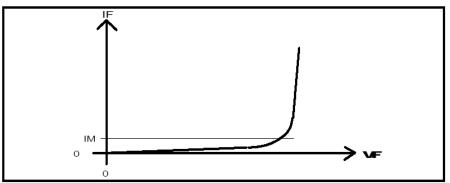

### How to select measurement current? TSP calibration

### How to select the $I_M$ measurement current?

- Guidelines in the JEDEC JESD51-1 document basically apply to the "dynamic" test method

- large enough to obtain reliable forward voltage reading (avoiding e.g. surface leakage effects)

- small enough to avoid possible self-heating effect

- Large difference between  $I_H$  and  $I_M$  currents allows easier  $\Delta V_F$  reading with less accurate test equipment not an issue for Mentor Graphics MicReD T3Ster equipment

- Self-heating is not an issue in Mentor Graphics MicReD's differential approach

temperature dependent variability between diodes of the same construction and size) the current is

temperature dependent variability between diodes of the same construction and size) the current is rarely chosen below 100  $\mu$ A and is usually 1 mA. The upper limit on  $I_M$  is determined by self-heating effects, which in turn are a function of the diode geometry.

Figure 1. - I<sub>M</sub> selection relative to typical diode I-V Curve

The measurement current (sensor current) must be chosen such that we remain in the "knee" of the diode characteristic.

### How to select the $I_M$ measurement current?

Recall the "static" test method

$$\Delta P_H(t+) = (I_H - I_M) \cdot V_{F0} + I_M \cdot \Delta V_F(t+)$$

$$Error < 1\% \Rightarrow \text{negligible}$$

$$I_{M}$$

=100 mA  $I_{H}$ =500 mA

$V_{F0}$ =800 mV  $\Delta T$ =50°C  $K$ =0.5 °C/mV  $\Rightarrow \Delta V_{F}$ =0.5 · 50=25 mV

$\Delta P_{H}$  = (0.5-0.1)·0.8 W= 320 mW  $I_{M}$ ·  $\Delta V_{F}$  = 0.1·0.025 W = 2.5 mW

Self-heating due to  $I_M$  is a myth; power error term caused by 100 mA current is below 1%

### How to select the $I_M$ measurement current?

Recall the static test method:

Higher  $I_M$  current provides advantages:

less disturbing electrical transients

Higher  $I_M$  – smaller electrical transient

A. Poppe & G. Farkas: Transient Measurements...

14 March 2016

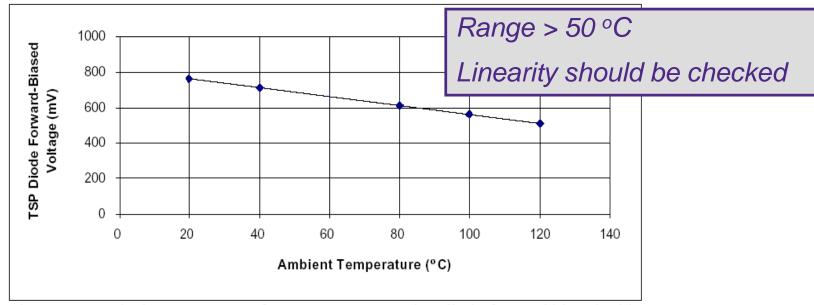

### K-factor calibration according to JESD51-1

Calibration should take place by applying the same I<sub>M</sub> current as during the tests

Figure 11. Typical  $V_F$  -  $T_A$  curve for temperature-sensing diode forward biased with  $I_M$ .

$$\Delta T = \Delta V_F \cdot K$$

$$S_{VF} = 1/K$$

$$K = \frac{\left(T_{Hi} - T_{Lo}\right)}{\left(V_{Hi} - V_{Lo}\right)}$$

$$_{(9)}$$

[°C/mV]

where  $T_{Hi} \& T_{Lo} = High \& Low temperatures [°C]$  $V_{Hi} \& V_{Lo} = corresponding High \& Low TSP voltages [mV]$

### Recommended setup for calibration and actual test

### TSP calibration setup with a fluid-bath thermostat

- Device calibration to identify the sensitivity of TSP.

- The ambient surrounding the DUT should have uniform temperature.

14 March 2016

# **Environmental** conditions

### JEDEC standard test conditions

- Besides test equipment, standard test conditions need to be provided

- test environments

- natural convection

- forced convection

- cold plate

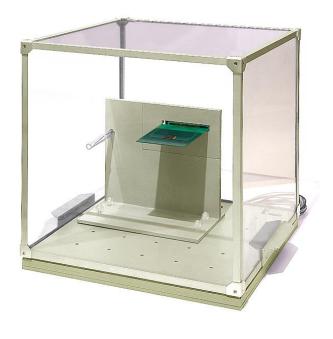

Natural convection: JEDEC JESD51-2A standard

Forced convection: JEDEC JESD51-6 standard

device fixtures / test boards

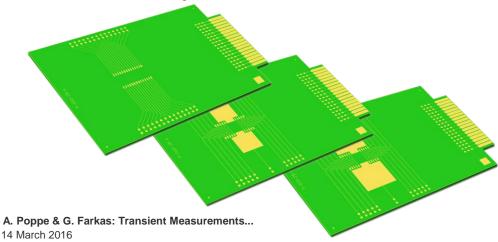

Different test boards: JEDEC JESD51-3, 5, 7, 10, 11

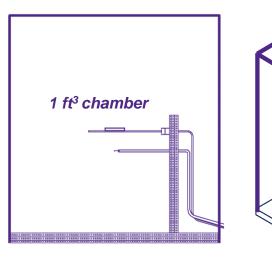

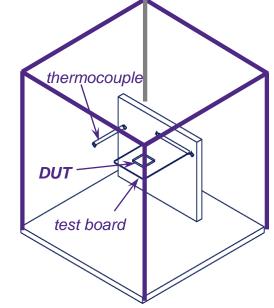

### Still-air chamber Thermal Transient Tester

Source of image http://www.utacgroup.com/technology\_contents\_analysis2.html

### Still-air chamber / test board definitions examples

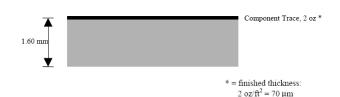

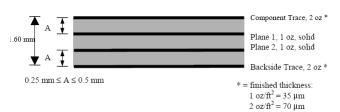

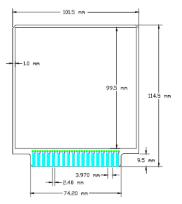

### JEDEC JESD51-2A standard

Low conductivity chamber material (e.g. polycarbonat)

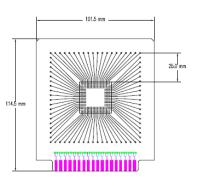

### JEDEC JESD51-11 standard

Figure 1a — Cross section of 1s PCB showing trace and dielectric thicknesses in package placement and trace fan-out regions

Figure 1b — Cross section of 2s2p PCB showing trace and dielectric thicknesses

| Table 1 — PCB sizes for package | ges |

|---------------------------------|-----|

|---------------------------------|-----|

| Package Length              | PCB Size (+/- 0.25 mm)                |

|-----------------------------|---------------------------------------|

| Pkg. Length ≤ 40 mm         | 101.5 mm x 114.5 mm (4.0 in x 4.5 in) |

| 40 mm < Pkg. Length ≤ 65 mm | 127.0 mm x 139.5 mm (5.0 in x 5.5 in) |

| 65 mm < Pkg. Length ≤ 90 mm | 152.5 mm x 165.0 mm (6.0 in x 6.5 in) |

Figure 2 - Example test board outer dimensions and edge connector design

Figure 3 - Traces to outer pin row flared to perimeter 25 mm from package body.

### JEDEC standard still-air chamber

- The chamber temperature must be measured according to the JEDEC standard

- It does not change too much when the transient extension of the static test method is used (max. variation is 0.2 °C in all practical cases)

- no need to use this data except that

- it is a good indicator if there is any odd air-flow inside the chamber

- indicates other problems like air-heating due to e.g. direct sunshine

as shown before, it cancels from our equations

### JEDEC standard test conditions

### Test environments

- natural convection: 1 ft<sup>3</sup> still-air chamber: **JESD51-2A** (2008)

- forced convection: wind tunnel **JESD51-6** (1999)

### Test boards

- copper coverage / number of layers - high / low conductivity, 1s / 2s

- different designs mathching different package styles

- design / orientation counts a lot, as shown by structure functions

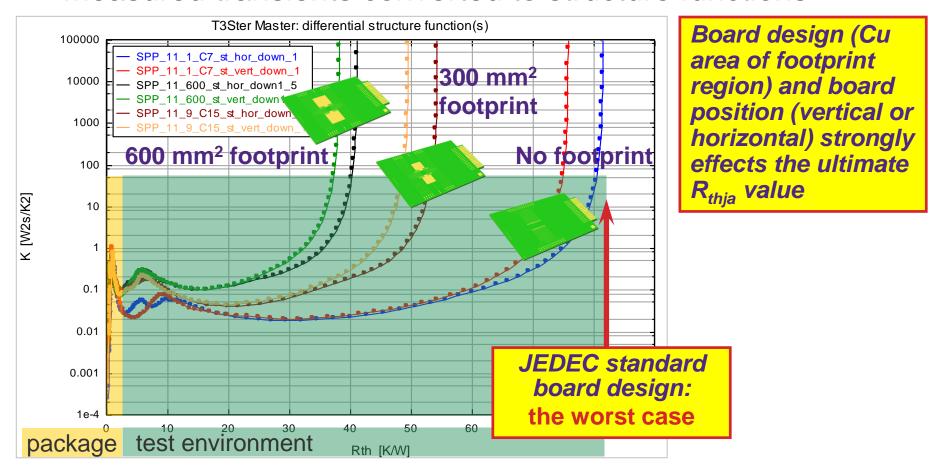

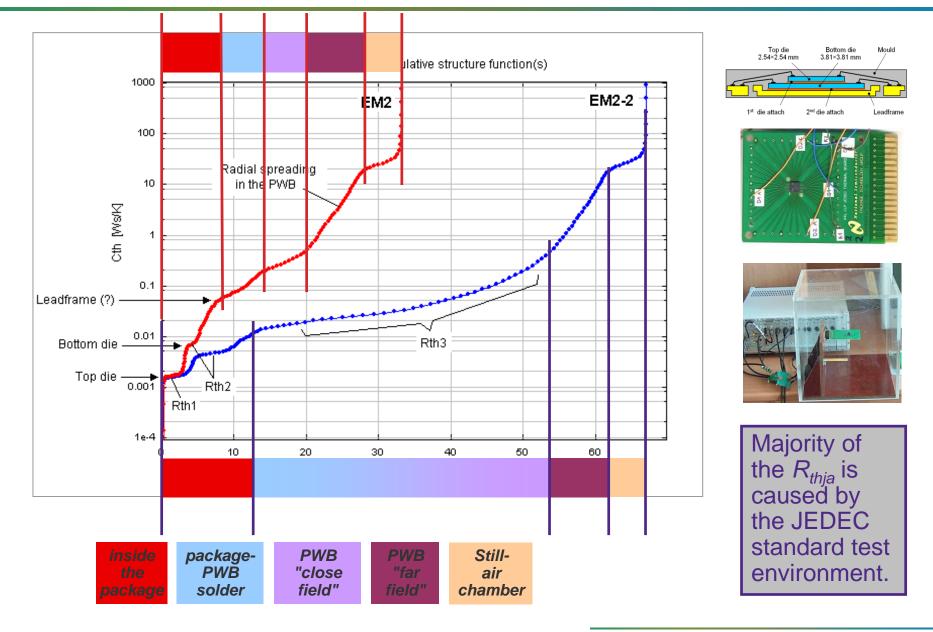

### Effect of test board design / orientation

- Tests performed in a JEDEC standard still-air chamber

- Measured transients converted to structure functions

- Measured R<sub>th</sub> is mostly due to the test environment

- measure on cold plate if possible, it is also faster

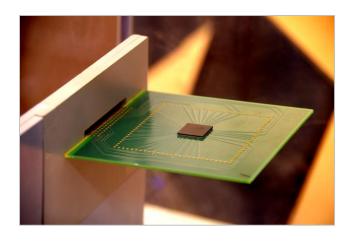

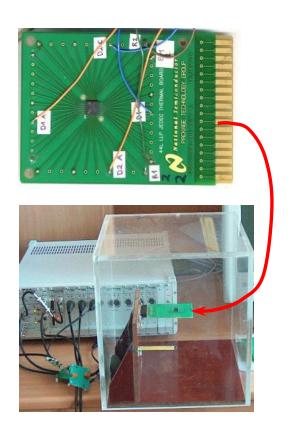

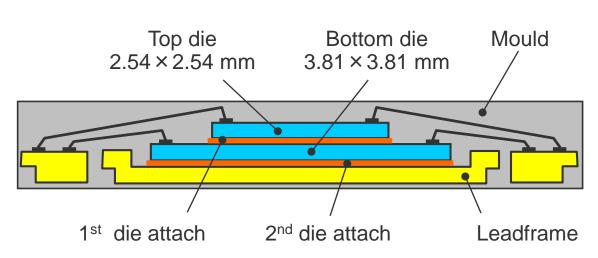

### Two live chips stacked in a 44L LLP package

- Stacked die package tested in JEDEC standard test environment

- Transient extension of the JESD51-1 static test method was used (T3Ster equipment), followed by structure function analysis

### Results in terms of structure functions

### Cold plate as a test environment

- Single cold plate setups for R<sub>thJC</sub> measurements

- also, test based models of power packages (transient extended JEDEC 2R models)

- LED testing

- Quicker test, shorter heat-flow path, results are characteristic to the package

- Dual cold plate setups for DELPHI boundary conditions

- validation of detailed models of test set of boundary conditions

- DCP1, DCP2, DCP3, DCP4 setups

### Test based model validation: for DELPHI models

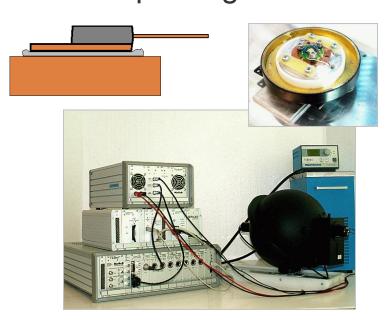

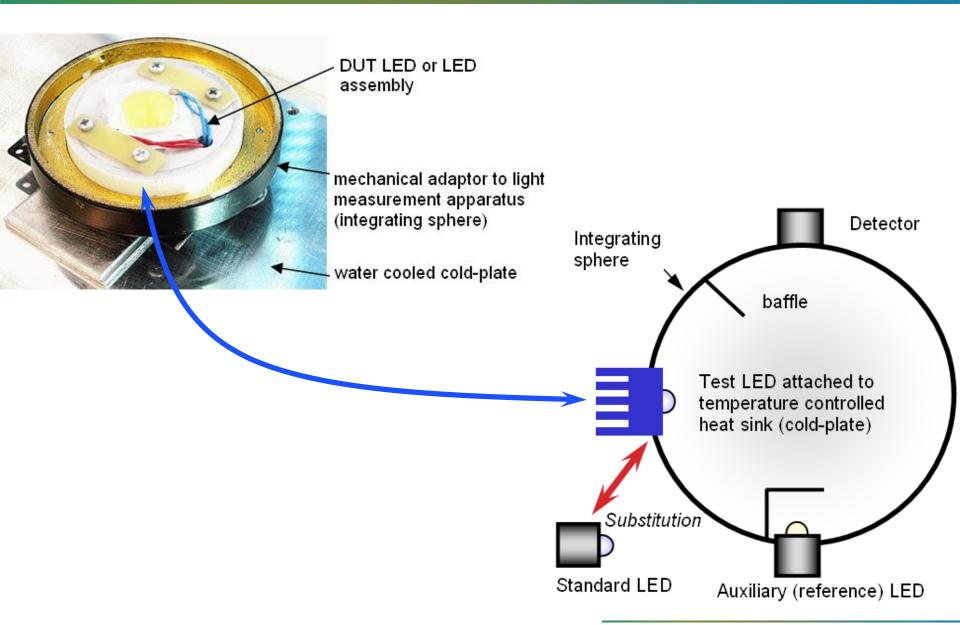

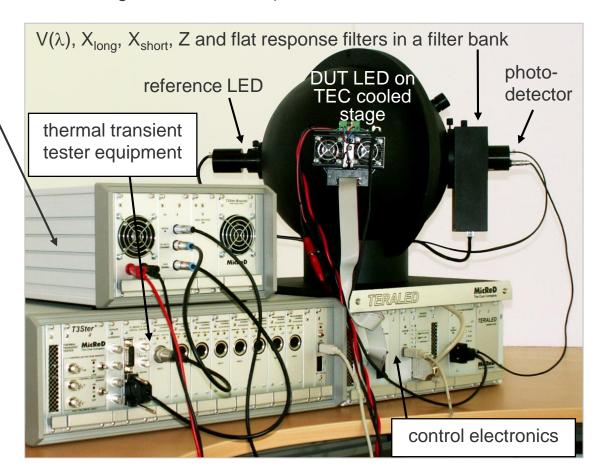

## Special environment for power LEDs: cold-plate and integrating sphere

### Test environment for LEDs: cold-plate and sphere

JEDEC JSD51-1 static test method compliant thermal measurement system

### Some details of the test environment

A. Poppe & G. Farkas: Transient Measurements...

### The Mentor Graphics MicReD implementation:

Special LED booster: allows high voltage across a LED line (overall forward voltage can reach 280V).

It can be added to the system in a plug&play manner if the voltage of the base tester is not sufficient.

### Case study: Thermal management solutions for a 10 W white LED

### Case study: 3 setups with Cree MCE 10W LEDs

- 3 different kinds of assemblies:

- FR4 PCB, TIM between the heat-slug and the Cu block

FR4 PCB, heat-slug soldered to the Cu block

MCPCB-s made of Al and Cu, heat-slug soldered

CAD images by courtesy of OptimalOptik Ltd. (Budapest, Hungary), measurements by Budapest University of Technology and Economics (BME).

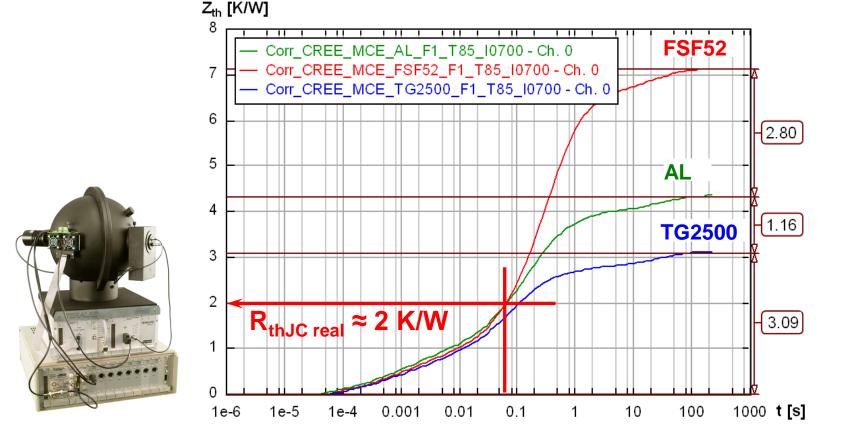

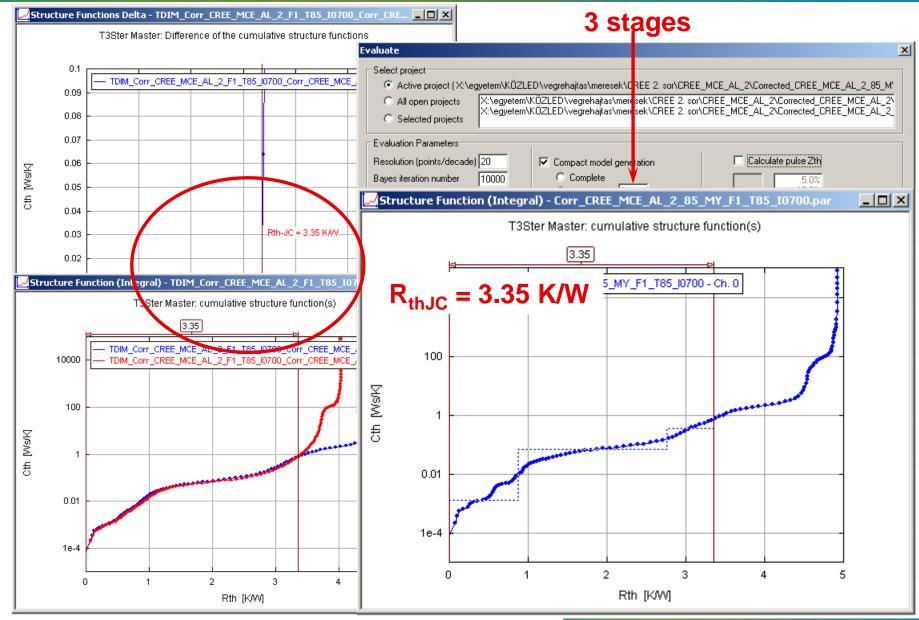

### Results for 10W Cree MCE white LEDs

- Measured at 700 mA and 85°C

- Thermal impedance of 3 samples, power corrected with P<sub>opt</sub>

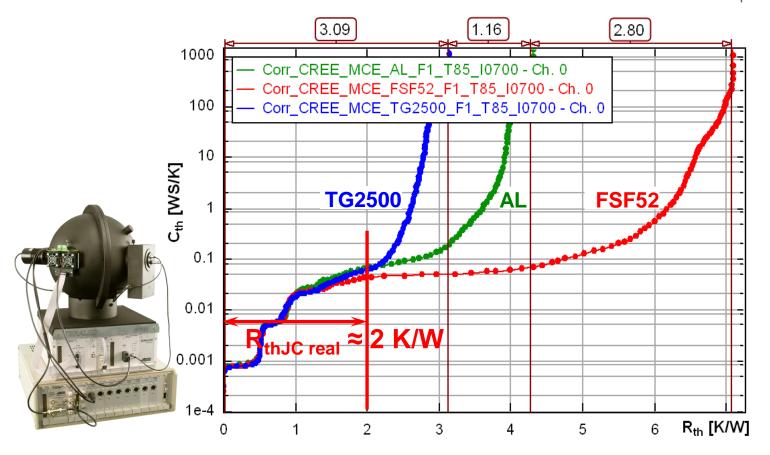

### Results for 10W Cree MCE white LEDs

- Measured at 700 mA and 85°C

- Structure functions of 3 samples, power corrected with P<sub>opt</sub>

R<sub>thJC</sub> is identified in a way similar to the *transient double interface method*, also being standardized by the JEDEC JC15 committee

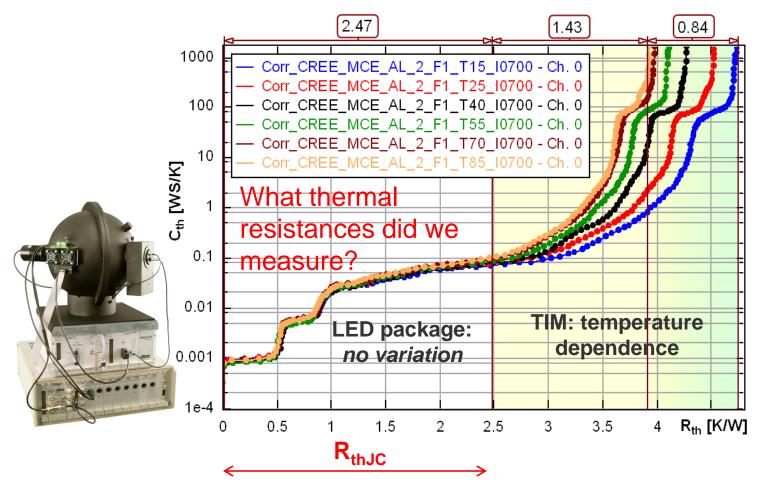

### Results for 10W Cree MCE white LEDs

- Measured at 350/700 mA & between 15°C and 85°C

- Structure functions of sample AL-2, power corrected with P<sub>opt</sub>

We measured the R<sub>thJC</sub> of the package and the TIM resistance

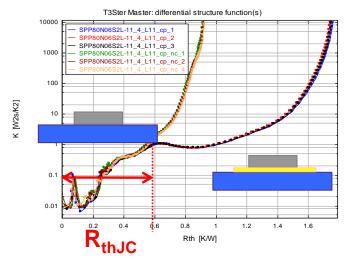

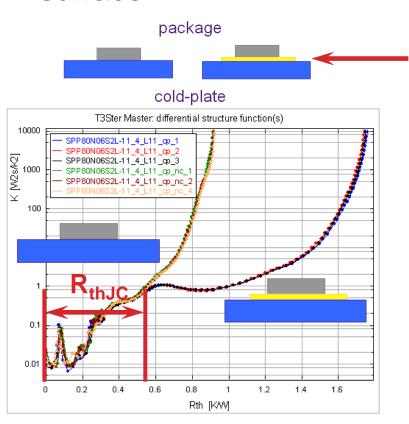

# The process of finding the R<sub>thJC</sub> value in T3Ster Master 2.x according to the new JEDEC standard JESD51-14

# The transient dual interface method for R<sub>thJC</sub>

- Original idea from 2005, standard JESD51-14 published in November 2010

- Change of thermal interface quality at the 'case' surface

- Divergence point in measured structure functions: 'case' surface

Change the quality of the thermal interface

Measurement of 2 setups (2x3 min), structure functions

# High accuracy and repeatability

- This type of  $R_{thJC}$  measurement provides high repeatability

- the continuous measurement of thermal transients is very reliable and highly repeatable if the setup is not changed

- repeatability is also high among different samples

- structure functions are derived from the transients by a mathematically well defined numerical procedure, thus, resulting structure functions are also highly repeatable

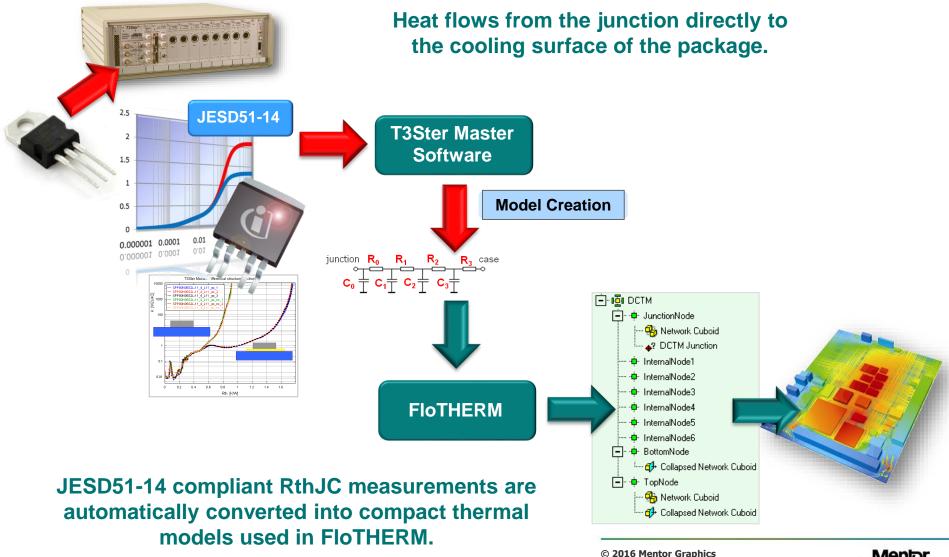

# Supporting thermal modeling

# Test based modeling and model validation

14 March 2016

A. Poppe & G. Farkas: Transient Measurements...

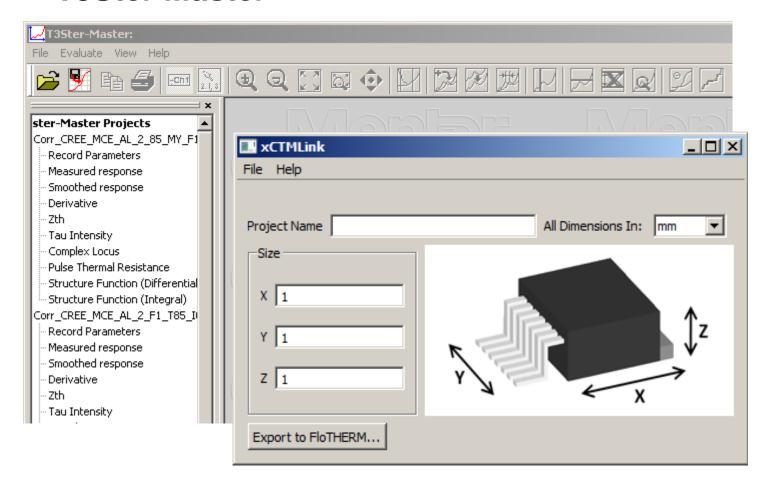

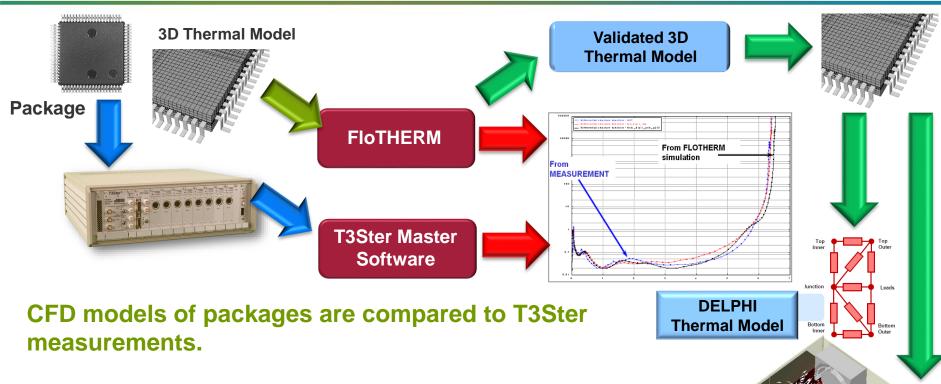

### **T3Ster Master** → **FIoTHERM Interface**

Compact thermal model of the heat-flow path is created by a step-wise approximation of the structure function

# Creating compact models in general

# Creating compact models for FloTHERM

Package geometry specified on file export from

T3Ster Master

### First and Unique Fully Automatic Measurement-**Based Modeling of Power Semiconductor Packages**

# First and Unique Measurement and Model Validation of IC Device Packages

Validated CFD model used to generate DELPHI compact models for FloTHERM & system level thermal analysis.

Alternatively the validated 3D thermal model may be used directly in FloTHERM

**FIOTHERM**

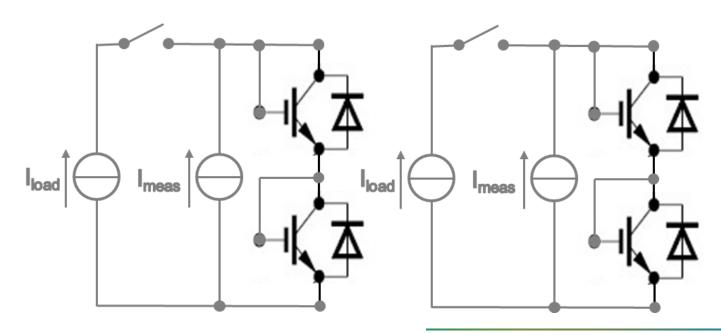

# Modeling and industrial QA analysis of IGBTs and other power component in the 1500 A ... 3000 A range

# Testing an IGBT module with kW level of power

- In power electronics industry both proper thermal design and reliability analysis of components such as IGBT modules is needed

- These tests need to be performed under realistic conditions

- 500 A ... 1500 A ... 3000 A of current needs to be supplied

- This results in multiple kW-s of heat to handle (needs proper cooling)

- MicReD industrial testing series of solutions

- Test conditions meet industrial requirements

- Powering

- Cooling

- Safety

- Automated tests

- Setup

- In-situ degradation monitoring

- Stop criteria

www.mentor.com/micred

# Test conditions for the half bridge modules

- Devices mounted on a cold-plate with highly stable thermal pad

- Gate and drain electrodes interconnected

- Common powering, but each device connected to a T3Ster channel

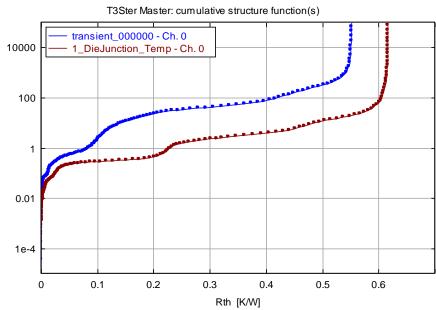

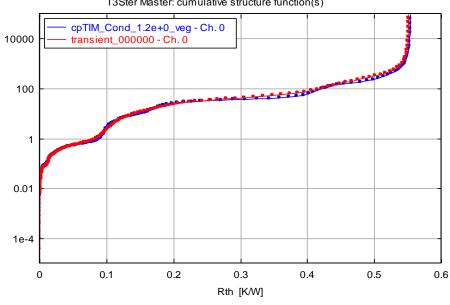

### Model calibration

### **Automated process in** FIOTHERM v11.

Learn about this in detail in Mentor Graphics' workshop

**How to Automatically Calibrate** FIoTHERM Package Models and Improve Thermal Design Reliability

15 March 2:00 p.m. - 3:00 p.m. (Fir)

### Initial model

Cth [Ws/K]

### Calibration steps:

- Die material parameters

- Die-source geometry

- Die attach resistance

- 4. Conductivity of the ceramics

- TIM between copper and cold-plate

### Calibrated model

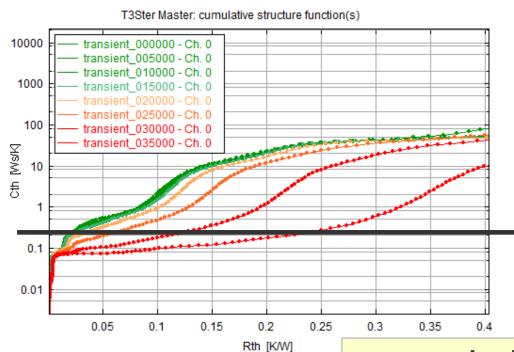

T3Ster Master: cumulative structure function(s)

Cth [Ws/K]

### **Powering conditions**

- Base plate temperature: 25° C

- Targeted junction temperature: 125° C

- Input power: 200W @ 25A

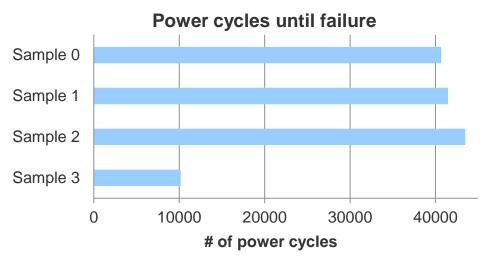

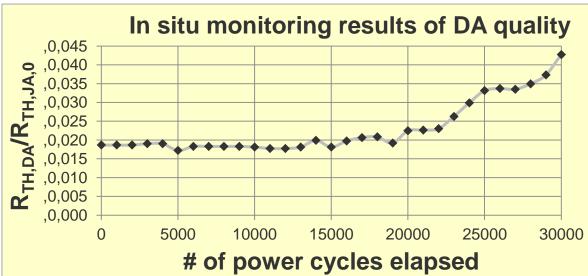

# Results of the reliability tests

The power cycling was conducted until the total failure of the IGBT-s

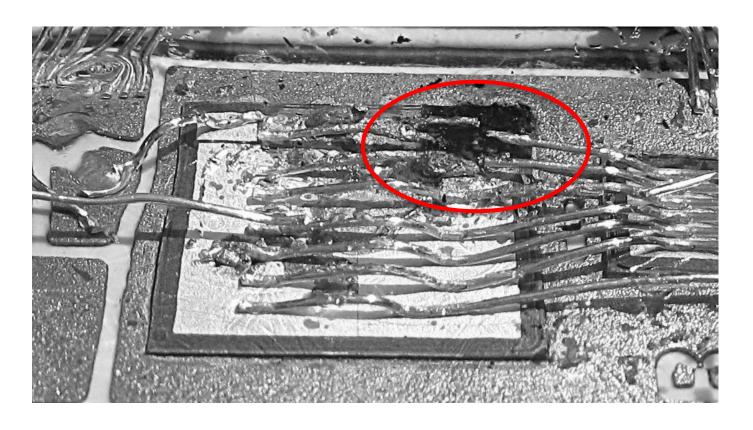

### Failures identified by visual inspection

- Broken bond-wires and burnt areas on the chip surface

- In face all IGBT-s failed due to the overheating and damage of the gateoxide

### **Further failure analysis**

Structure functions obtained in situ during power cycling

# Results of visual inspection

- Broken bond-wires and burnt areas on the chip surface

- In face all IGBT-s failed due to the overheating and damage of the gate-oxide

# Structure functions showing die-attach degradation

# **Further information**

### Recommended reading:

For more details and references of the topics covered in this course please refer to

Chapter 4 <u>Thermal Testing of LEDs</u> (G. Farkas, A. Poppe) of a recent book C.J.M. Lasance – A. Poppe (eds): <u>Thermal Management for LED Applications</u>, September 2014, <u>Springer</u>

http://www.springer.com/engineering/electronics/book/978-1-4614-5090-0