Available online at www.sciencedirect.com

MATERIALS SCIENCE IN SEMICONDUCTOR PROCESSING

PERGAMON

Materials Science in Semiconductor Processing I (IIII) III-III

# Future roadblocks and solutions in silicon technology as outlined by the ITRS roadmap $\stackrel{\text{\tiny{themselve}}}{\to}$

Wolfgang Arden\*

Infineon Technologies AG, St. Martin Strasse 76, D 81541 München, Germany

#### Abstract

The International Technology Roadmap for Semiconductors (ITRS) is a joint global effort of the semiconductor industry and research community to define the future development and requirements of the semiconductor technology for the next 15 years. The paper will review the major challenges, potential roadblocks and proposed solutions for the industry as outlined in the ITRS 2001. The major sections of the ITRS contain technical information about frontend processing and interconnect, device structures and memory concepts, lithography and metrology as well as factory integration and environmental issues. Specific emphasis is given to describe future requirements on new materials and material properties as well as topics related to silicon wafer sizes of 300 mm and beyond. Special issues will be addressed, for example new transistor gate materials, new solutions for interconnect beyond copper metals and low kdielectrics as well as new starting materials for wafer sizes beyond 300 mm.

© 2003 Elsevier Science Ltd. All rights reserved.

Keywords: Silicon technology; Roadmap; Semiconductors; Devices; New materials

### 1. Introduction

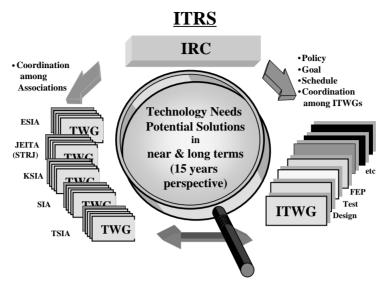

The definition of a technology roadmap for the semiconductor industry has started as a national effort in the United States in 1992. Six years later this effort became an international activity with the major global regions participating in the definition of the roadmap, which is now called the International Technology Roadmap for Semiconductors (ITRS [1]). The mission of the ITRS is to define the near and long-term technology requirements for the semiconductor industry as well as to outline potential solutions to meet these needs, as described in Fig. 1. There are 12 International Technical Working Groups (ITWG) with over 800 experts dealing with key areas of the semiconductor technology as there are, e.g. Design and Test, Front End Processing, Interconnect, Lithography, Process Integra-

\*Tel.: +49-89-234-41480; fax: +49-89-234-717-959.

tion and others. The overall activity of the ITRS is coordinated by an International Roadmap Committee (IRC).

### 2. Hierarchy of IC Requirements

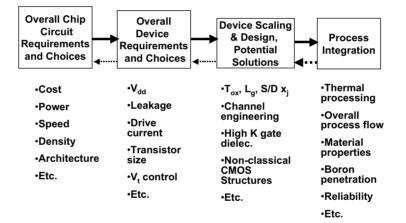

In order to define the technology demands of the IC industry, a hierarchy of requirements is established in the ITRS, as outlined in Fig. 2. This process starts with the definition of chip circuit requirements like cost, power, speed and density followed by overall device requirements given by the parameters supply voltage, leakage and drive currents, transistor sizes, threshold voltage control and others. Thereafter device scaling and device design issues are defined as for example gate length, gate dielectric, junction depth, channel engineering properties and finally process integration requirements are resulting, e.g. thermal budget, overall process flow and material properties. In order to define this sequence of technology needs, a very intensive crossfunctional cooperation between the individual Technical Working Groups has become a common practice.

$<sup>^{*}</sup>$  This paper was presented as an invited paper in the 300 mm session of the 2002 spring conference of the European Materials Research Society (EMRS) in Strasbourg, 18-21 June.

E-mail address: wolfgang.arden@infineon.com (W. Arden).

W. Arden | Materials Science in Semiconductor Processing I (IIII) III-III

Fig. 1. Mission and definition process for ITRS.

Fig. 2. Hierarchy of IC requirements and choices.

#### 3. Challenges and solutions for device scaling

The continuous scaling of classical CMOS devices is building up key challenges for the design of the transistor. The down scaling of the supply voltage requires an accelerated shrink of the gate length in order to keep up with the demands for drive currents and speed; the scaling of the gate length however results in an increase of the gate resistance with the demand to introduce low resistivity/metal gates, e.g. SiGe gates, especially for RF applications. The scaling of the gate oxide thickness leads to an increase of tunneling currents which results in unacceptable leakage currents and requires the introduction of high k dielectrics as, e.g. oxinitrides or oxide-based compounds of Aluminum/ Hafnium. The third area with device scaling leading to

severe limitations, is the source/drain region where the continuous thickness reduction results in high series resistance and problems in silicidation with the demand for innovative solutions as, e.g. elevated source/drain. Some of these issues are highlighted in Fig. 3. The table depicts some values of gate stack requirements over time as there are gate lengths for MPUs and Low Power ASICs with the corresponding Equivalent Oxides Thicknesses (EOT) and the allowed gate leakage currents. The red-shaded numbers in the ITRS table indicate that there are no technical solutions yet available, whereas yellow-shaded numbers mean that technical solutions are known, but not yet manufacturable. Numbers in white fields denote the status of manufacturability for the respective required value.

Direct tunneling currents limit allowable <u>gate oxide</u> thickness reduction, thereby limiting gate capacitance and gate control over channel charge Electrical depletion of doped polysilicon results in unwanted parasitic capacitance that limits gate control of channel charge, ultimately requiring <u>metal gates</u>

| I                                                                              |         |         | _/       |         |          |          |          |

|--------------------------------------------------------------------------------|---------|---------|----------|---------|----------|----------|----------|

| Year of Production                                                             | 2001    | 2002    | 2003     | 2004    | 2005     | 2006     | 2007     |

| Technology Node (nm) (also equals DRAM 1/2 Pitch)                              | 130     | 115     | 100      | 90      | 80       | 70       | 65       |

| MPU/ASIC High Performance Gate Length (nm)                                     | 65      | 53      | 45       | 37      | 32       | 28       | 25       |

| Low Power Gate Length (nm)                                                     | 90      | 80      | 65       | 53      | 45       | 37       | 32       |

| Equivalent Physical Oxide Thickness, EOT, (nm)                                 | 1.3-1.6 | 1.2-1.5 | 1.1-1.5  | 0.9-1.4 | 0.8-1.3  | 0.7-1.2  | 0.6-1.1  |

| Low Operating Power EOT (NM)                                                   | 2.0-2.4 | 1.8-2.2 | 1.6-2.0  | 1.4-1.8 | 1.2-1.6  | 1.1-1.5  | 1.0-1.4  |

| Low Standby Power EOT (NM)                                                     | 2.4-2.8 | 2.2-2.6 | 2.0-2.4  | 1.8-2.2 | 1.6-2.0  | 1.4-1.8  | 1.2-1.6  |

| High Performance Allowable Gate Leakage (A/cm <sup>2</sup> )                   | 15      | 57      | 156      | 270     | 938      | 2500     | 4000     |

| Low Strandby Power Allowable Gate Leakage (A/cm <sup>2</sup> )                 | 0.0011  | 0.0013  | 0.0015   | 0.0019  | 0.0022   | 0.0027   | 0.0031   |

| Active Gate Polysilicon Doping for 25% Depletion Allowance (cm <sup>-3</sup> ) | 9.2 E19 | 9.2 E19 | 1.14 E20 | 1.5 E20 | 1.66 E20 | 1.66 E20 | 1.87 E20 |

### "red wall" for high performance results from reliability and thickness control

### "red wall" for low power results from lower allowed tunneling curents

Fig. 3. Gate stack challenges.

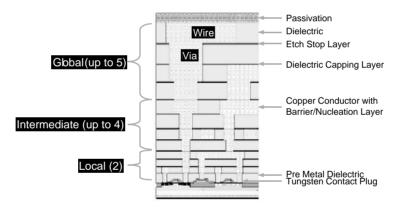

Fig. 4. Chip cross-section illustrating hierarchical interconnect scaling.

On the long term the device architecture for CMOS devices has to be modified in order to meet future device requirements. For example, non-standard double-gate MOSFET devices may have to be introduced as early as in the year 2007. This and other approaches of non-classical CMOS devices will be discussed in the 6th chapter.

Another issue concerning the frontend processing in general will be the introduction of silicon starting materials beyond 300 mm: For reasons of productivity enhancement, the introduction of the next generation wafer size of 450 mm is expected for the year 2014. Cost effective up-scaling of the incumbent Czochralzki crystal pulling and wafer slicing process is questionable and may need new solutions.

### 4. Interconnect issues

Fig. 4 depicts a typical chip cross-section with a metalization scheme illustrating the hierarchical scaling methodology with local wiring, intermediate wiring and global wiring resulting in up to 10 metalization levels in an advanced chip technology. The total interconnect length with active wiring excluding global levels will amount up to about  $10.000 \text{ m/cm}^2$  chip area in the year 2005 and beyond. The increase in wiring length puts an enormous challenge to the constant reliability requirement in failures in time (FIT) values.

On the near term (next 5 years) the increasing effect of interconnect parasitic capacitances leads to the need for integrating interconnect dielectrics with low dielectric

| YEAR<br>TECHNOLOGY NODE                                                                                                    | 2010    | 2013    | 2016    |

|----------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|

| DRAM ½ PITCH (nm) (SC. 2.0)                                                                                                | 45      | 32      | 22      |

| MPU/ASIC ½ PITCH (nm) (Sc. 3.7)                                                                                            | 45      | 32      | 22      |

| MPU PRINTED GATE LENGTH (nm) (Sc. 3.7)                                                                                     | 25      | 18      | 13      |

| MPU PHYSICAL GATE LENGTH (nm) (SC. 3.7)                                                                                    | 18      | 13      | 9.0     |

| Number of metal levels                                                                                                     | 10      | 11      | 11      |

| Total interconnect length (m/cm <sup>2</sup> ) – active wiring only,<br>excluding global levels (footnote for calculation) | 16063   | 22695   | 33508   |

| Local wiring pitch (nm)                                                                                                    | 105     | 75      | 50      |

| Local A/R (for Cu)                                                                                                         | 1.8     | 1.9     | 2.0     |

| Intermediate wiring pitch (nm)                                                                                             | 135     | 95      | 65      |

| Intermediate wiring dual damascene A/R (Cu wire/via)                                                                       | 1.8/1.6 | 1.9/1.7 | 2.0/1.8 |

| Minimum global wiring pitch (nm)                                                                                           | 205     | 140     | 100     |

| Global wiring dual damascene A/R (Cu wire/via)                                                                             | 2.3/2.1 | 2.4/2.2 | 2.5/2.3 |

| Cu thinning global wiring due to dishing (nm),<br>100 micron wide feature                                                  | 14      | 10      | 8       |

| Conductor effective resistivity<br>(μΩ-cm) Cu intermediate wiring*                                                         | 2.2     | 2.2     | 2.2     |

| Barrier/cladding thickness<br>(for Cu intermediate wiring) (nm)***                                                         | 5       | 3.5     | 2.5     |

| Interlevel metal insulator—effective dielectric constant (κ)                                                               | 2.1     | 1.9     | 1.8     |

| Interlevel metal insulator (minimum expected)<br>—bulk dielectric constant (κ)                                             | <1.9    | <1.7    | <1.6    |

Fig. 5. Long-term interconnect requirements for microprocessors.

constants. The corresponding k values will be decreasing from 3.6 today down to about 2 and below in the year 2007 and beyond. Due to severe material and integration problems the introduction of so-called low k dielectrics has been delayed in the ITRS 2001 edition as compared to the 1999 version. On the longer term the key challenges for interconnects will be the limited conductivity of the present conductor material copper. Fig. 5 highlights the requirements on wiring pitch, aspect ratio, conductor resistivity, barrier thickness and insulator dielectric value for microprocessors for the years 2010 to 2016. The numbers in red indicate that new solutions beyond the present technology have to be developed and introduced. Material innovation combined with traditional scaling will no longer satisfy the performance requirements. New innovative concepts in the areas of design, interconnect and packaging are needed to overcome the limited conductivity of the copper interconnect material in longer term. Alternative conductors may have to be introduced, as for example optical or RF conductors.

#### 5. Material requirements

The future development of the IC industry puts forward major challenges to the material research

scientists. Although silicon substrate materials will remain the dominant material in the IC industry for the next 15 years, both physical and technological limitations are demanding for the introduction of new materials both in the frontend as well as in the interconnect/backend processing area of the semiconductor technology. Fig. 6 highlights the key issues of new material requirements in silicon technology as outlined in the ITRS 2001. ASIC and microprocessor applications are pushing the material innovation in the gate stack and interconnect technology, whereas in the memory area the continuous scaling of memory cell sizes drives the introduction of high k dielectric materials for DRAMs and ferroelectric materials for Non-Volatile Memories. In lithography new materials will be required for imaging resists as well as for mask substrates and projection lens elements, as for example CaF<sub>2</sub> for 157 nm projection.

The silicon substrate itself has a variety of both mechanical and chemical requirements which get more demanding with further scaling of the semiconductor technology and the introduction of larger wafer sizes. Key numbers for those parameters are defined in the ITRS and summarized in Fig. 7. Mainly the defect specifications for layer structural defects, buried oxide defects and gate oxide integrity are getting very tight in future years, thereby challenging both the research scientist and the process engineer.

W. Arden | Materials Science in Semiconductor Processing I (IIII) III-III

| High k Gate:        | AI                                                            | 203          | Silicates<br>Unary Oxide |                | s/Single Crys |      |

|---------------------|---------------------------------------------------------------|--------------|--------------------------|----------------|---------------|------|

|                     | k=                                                            | 510          | k=1020                   |                | k>20          |      |

| High Mobility Cha   | nnel                                                          | Straine      | d SiGe                   |                |               |      |

| Gate                | Silicide/Poly                                                 | SiGe         | Dual Me                  | etal Gate Elec | trodes        |      |

| High k dielectric : | Ta <sub>2</sub> O <sub>5</sub> Al <sub>2</sub> O <sub>3</sub> |              |                          |                |               |      |

| for DRAM            |                                                               | BST ST       | O Epi BS                 | т              |               |      |

| NVM/Integr. Passi   | ves                                                           | BST          |                          |                |               |      |

| Low k IMD (eff.)    | 2.5                                                           | 3.1 2        | .22.7                    | 2.1            | 1.9           | 1.8  |

| FRAM Materials      |                                                               |              |                          |                |               |      |

| Litho:              | CaF <sub>2</sub> Subst                                        | rate for Opt | ical Masks               |                |               |      |

|                     | 157nr                                                         | n Pellicle   |                          |                |               |      |

| Substrate           |                                                               |              | 450mm s                  | ilicon substra | ite           |      |

| 1:                  | 30nm 90                                                       | )nm          | 65nm                     | 45nm 3         | 32nm :        | 22nm |

| 2                   | 001 20                                                        |              |                          | 2010 2         |               | 016  |

Technology Node Introduction

Fig. 6. Material requirements for front- and back-end processes.

| Wafer Diameter                                                    | 200            | 300                 | 300                       | 300                       | 450             | 450             |

|-------------------------------------------------------------------|----------------|---------------------|---------------------------|---------------------------|-----------------|-----------------|

| Crit. Surface Metal<br>(10 <sup>9</sup> at/cm²)                   | <18            | <12                 | <5.8                      | <4.2                      | <3.6            | <3.4            |

| Site Flatness<br><sup>(nm)</sup>                                  | < 180          | < 150               | < 110                     | < 70                      | < 50            | < 35            |

| Crystal Orig. Pits<br>COPs (#/wafer)                              | < 38           | < 78                | < 84                      | < 73                      | < 170           | < 165           |

| Particles (#/cm²)<br>Particles (#/wafer)                          | < 0.13<br>< 38 | < 0.12<br>< 78      | < 0.12<br>< 84            | <0.10<br>< 73             | < 0.10<br>< 170 | < 0.10<br>< 165 |

| Layer Structural<br>Defects<br>for EPI (MPU) (#/cm <sup>2</sup> ) | < 0.018        | <0.018<br>(large ar | <0.018<br>ea defect + sta | < 0.018<br>acking faults) | < 0.018         | < 0.018         |

| Buried Oxide Defects<br>for SOI (MPU) (#/cm <sup>2</sup> )        | < 0.359        | < 0.352             | < 0.254                   | < 0.154                   | < 0.107         | < 0.080         |

| BOX Thickness (nm)                                                | < 200          | <200                | <100                      | < 70                      | <50             | <50             |

| SOI - Si Device Layer                                             | 30-200         | 30-200              | 20-100                    | 20-100                    | 20-100          | 20-100          |

| Gate Oxide Integrity                                              | 0.1            | 0.08                | 0.05                      | 0.042                     | 0.023           | 0.023           |

| (Logic)#/cm²                                                      | 180nm<br>1999  | 130nm 10<br>2002    | 2005                      | e Introductio             | 40nm<br>2011    | 30nm<br>2014    |

|                                                                   |                | rechin              | ology Nou                 |                           |                 |                 |

Fig. 7. Material requirements for silicon substrates.

### 6. Novel devices

The traditional scaling of classical CMOS devices leads to performance limitations which have to be overcome by introduction of new materials and improvements of the device design as has been mentioned in the 3rd chapter. However, planar conventional CMOS devices cannot be scaled to dimensions below 50 nm gate lengths without severely sacrificing performance. New, so-called "non-classical" device concepts are being developed for MOS devices to remove the barriers of conventional MOS transistor designs. An overview on some of these new-still CMOS-based-device concepts, their architectures, their advantages and challenges are described in Fig. 8. Whereas silicon-oninsulator (SOI) devices are already being introduced for high-performance applications, the implementation of less conventional MOS device architectures as for example vertical and double-gate transistors still need more engineering work for about 5–10 years, before all manufacturing issues will be solved.

#### 7. Summary

The methodology and the hierarchical approach of the definition of future requirements of the IC industry in the ITRS have been described. Major limitations in overall chip performance as imposed by conventional CMOS scaling can be overcome by the introduction of new materials in both the frontend and interconnect processing area together with more sophisticated device

W. Arden | Materials Science in Semiconductor Processing I (IIII) III-III

|                    |                                                                                       |                                                                                    | Gate Gate Drain                                                                                                                     |                                                                                                         | units of fa                                                                                                                                  |  |  |

|--------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DEVICE             | ULTRA-THIN BODY SOI                                                                   | BAND-ENGINEERED<br>TRANSISTOR                                                      | VERTICAL TRANSISTOR                                                                                                                 | FINFET                                                                                                  | Double-Gate<br>Transisto                                                                                                                     |  |  |

| Concept            | Fully depleted SOI                                                                    | SiGe or Strained Si<br>channel; bulk Si or<br>SOI                                  | Double-gate or surround-gate structure<br>(No specific temporal sequence forthese three structure<br>intended)                      |                                                                                                         |                                                                                                                                              |  |  |

| APPLICATION/DRIVER | Hig                                                                                   | her performance, Higher                                                            | transistor density, Low                                                                                                             | ver power dissipation                                                                                   |                                                                                                                                              |  |  |

|                    | Improved                                                                              |                                                                                    | -Higher drive                                                                                                                       | -Higher drive<br>current<br>-Improved                                                                   | -Higher drive<br>current<br>-Improved                                                                                                        |  |  |

| Advantages         | -Improved<br>subthreshold slope<br>V <sub>t</sub> controllability                     | -Higher drive current<br>-Compatible with<br>bulk and SOI CMOS                     | current<br>Lithography<br>independent Lg                                                                                            | subthreshold<br>slope<br>-Improved short<br>channel effect<br>-Stacked NAND                             | subthreshold<br>slope<br>-Improved short<br>channel effect<br>-Stacked NAND                                                                  |  |  |

| Scaling Issues     | -Si film thickness<br>-Gate stack<br>-Worse short channel<br>effect than bulk<br>CMOS | -High mobility film<br>thickness, in case of<br>SOI<br>-Gate stack<br>-Integration | -Si film thickness<br>-Gate stack<br>-Integrability<br>-Process<br>complexity<br>-Accurate TCAD<br>including QM                     | -Si film thickness<br>-Gate stack<br>-Process<br>complexity<br>-Accurate TCAD<br>including QM<br>effect | -Gate alignment<br>-Si film thickness<br>-Gate stack<br>-Integrability<br>-Process<br>complexity<br>-Accurate TCAD<br>including QM<br>effect |  |  |

| Design Challenges  | -Device<br>characterization<br>-Compact model and<br>parameter extraction             | -Device<br>characterization                                                        | -Device characterization<br>-PD versus FD<br>-Compact model and parameter extraction<br>-Applicability to mixed signal applications |                                                                                                         |                                                                                                                                              |  |  |

| MATURITY           |                                                                                       |                                                                                    | Development                                                                                                                         |                                                                                                         |                                                                                                                                              |  |  |

| Timing             | Near Future                                                                           |                                                                                    |                                                                                                                                     |                                                                                                         |                                                                                                                                              |  |  |

| Fig 8    | Cross | sections | and | characteristics | of | non-classical | CMOS | devices  |

|----------|-------|----------|-----|-----------------|----|---------------|------|----------|

| 1 1g. o. | C1055 | sections | anu | characteristics | oı | non-classical | CMOS | ucvices. |

# Moving Closer to the "Red Brick Wall" ITRS 2001 Results

Challenges/Opportunities for Semiconductor R&D

| Year of Production:                | 2001    | 2003    | 2005    | 2007    | 2010    | 2016    |

|------------------------------------|---------|---------|---------|---------|---------|---------|

| DRAM Half-Pitch [nm]:              | 130     | 100     | 80      | 65      | 45      | 22      |

| Overlay Accuracy [nm]:             | 46      | 35      | 28      | 23      | 18      | 9       |

| MPU Gate Length [nm]:              | 90      | 65      | 45      | 35      | 25      | 13      |

| CD Control [nm]:                   | 8       | 5.5     | 3.9     | 3.1     | 2.2     | 1.1     |

| T <sub>ox</sub> (equivalent) [nm]: | 1.3-1.6 | 1.1-1.6 | 0.8-1.3 | 0.6-1.1 | 0.5-0.8 | 0.4-0.5 |

| Junction Depth [nm]:               | 48-95   | 33-66   | 24-47   | 18-37   | 13-26   | 7-13    |

| Metal Cladding [nm]:               | 16      | 12      | 9       | 7       | 5       | 2.5     |

| Inter-Metal Dielectric K:          | 3.0-3.6 | 3.0-3.6 | 2.6-3.1 | 2.3-2.7 | 2.1     | 1.8     |

|                                    |         |         |         | Vi      |         |         |

Fig. 9. "Red Brick Wall" illustrating key challenges in future silicon technology.

engineering. Some of the key challenges of the shortand long-term needs of the ITRS are summarized in Fig. 9. All major issues are being addressed in the research and development areas of the industry and of research consortia to meet these requirements. On the long term new non-classical CMOS-based devices will be introduced to fulfil the continuous demand for performance increase and cost decrease of the IC industry. Silicon-based technology will be the mainstream semiconductor technology for at least the next 15 years.

### Acknowledgements

The provision of some of the figures of this article by Toshitaka Fukushima, Fujitsu Corporation, Werner Klingenstein, Infineon Technologies, and the Semiconductor Industry Association, who has the copyright of the contents of the ITRS, is highly appreciated.

### References

[1] ITRS Web-Site: http://public.itrs.net/