Microelectronic Engineering 30 (1996) 375-382

# Atom Electronics: A proposal of nano-scale devices based on atom/molecule switching

Yasuo Wada

Advanced Research Laboratory, Hitachi, Ltd. 2520 Akanuma Hatoyama, Saitama 350-03 Japan

This paper describes the possibility of atom/molecule switching devices, which are candidates to supersede the present metal-oxide-semiconductor (MOS) devices and to establish the new era of Atom Electronics. They are Atom Relay Transistors (ART) and Molecular Single Electron Switching (MOSES) devices, with total dimensions of a few nm and an operation speed of more than Tera ( $10^{12}$ ) Hz. Using these devices, it is estimated that a supercomputer, with  $10^7$  gates of logic circuit and  $10^9$  bits of memory, would be integrated in an area 200  $\mu$ m square and operating at more than Tera ( $10^{12}$ ) Hz. ART and MOSES devices are evaluated on the basis of the characteristics necessary for information processing integrated circuit devices, together with other nano scale devices, and are found to be the most promising candidates that supersede the present metal oxide semiconductor (MOS) devices for information processing in the next decade. This paper also describes several technologies which could contribute to the establishment of Atom Electronics, including beam assisted scanning tunneling microscope (BASTM) which makes it possible to observe insulator surfaces, micromachine scanning tunneling microscope ( $\mu$ -STM) by which the vacuum tunneling gap is successfully observed and the Needle Formation and Tip Imaging (NFTI) method which makes possible the in-situ evaluation of the tip apex of an STM.

### 1. Introduction

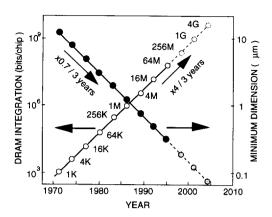

Information processing electronic devices have been taken over by higher performance devices. starting with relay, vacuum tube, transistor and integrated circuit, as shown in Table 1, all in the quest for much higher performance information processing. It has been historically proven that innovation of more than two orders of magnitude is indispensable for the paradigm shift of information processing devices. Today, almost all the information processing is achieved by silicon integrated circuits, because of their exceedingly high performance, exceptional reliability and surprisingly low cost. Advances in silicon integrated circuit technology have been made possible by the downscaling of metal oxide semiconductor (MOS) transistors [1]. This progress suggests that there are no limits to the microminiaturization of silicon technologies down to the nm level. However, several physical limitations might prove obstacles to further microminiaturization beyond the 0.1 µm technology level [2]. The down-scaling trend of MOS transistors used in large scale integrated circuits (LSI's) is shown in Fig. 1, which indicates that device integration per chip has increased by a factor of four every three years, while the minimum

Table 1 Comparison of historical and future information processing devices: human being started information processing by using relay, replacing with vacuum tube, transistor and integrated circuit, by the quest for higher performance computing

| DEVICE                      | RELAY                                   | VACUUM<br>TUBE                           | TRANSISTOR<br>INTEGRATED<br>CIRCUIT                          | ART<br>MOSES                         |

|-----------------------------|-----------------------------------------|------------------------------------------|--------------------------------------------------------------|--------------------------------------|

| THEORY/<br>ELECTRO-<br>NICS | ELECTRO-<br>MAGNE-<br>TICS<br>(Faraday) | VACUUM<br>ELECTRO-<br>NICS<br>(Thompson) | SOLID<br>STATE<br>ELECTRO-<br>NICS<br>(Bardeen,<br>Schokley) | ATOM<br>ELECTRO-<br>NICS             |

| TECH-<br>NOLOGY             | METAL<br>WORK<br>TECH-<br>NOLOGY        | VACUUM<br>TECH-<br>NOLOGY                | SEMICON-<br>DUCTOR<br>TECH-<br>NOLOGY                        | SCANNING<br>PROBE<br>TECH-<br>NOLOGY |

dimension has been reduced by a factor of 0.7 every three years. It also suggests that the minimum dimension of about  $0.1 \, \mu m$  might be reached around the year 2010. Therefore nano scale devices, such as quantum effect devices [3], have recently been attracting attention as candidates to supersede silicon MOS transistors. However, it is uncertain whether these "quantum" devices will be able to replace MOS transistors, which are almost ideal information processing devices, as will be discussed in the later section. As mentioned earlier, more than two orders

Fig.1 down-scaling trend of MOS transistor used in LSI's between the years 1970 and 1995, extrapolating to 2010.

of magnitude improvement in performance is indispensable for the paradigm shift, because otherwise the total performance would not be attractive enough to replace the total system.

This paper reports on the prospect of Atom Electronics and atom/ molecule scale information processing devices in the next decade, as indicated in Table 1. It proposes atom size switching devices, Atom Relay Transistors (ART) [4] and Molecular Single Electron Switching (MOSES) devices [5], with dimensions of a few nm, and an operation speed of more than  $10^{12}$  (Tera:T) Hz. The switching characteristics of ART are demonstrated by simulation and memory cell and logic gates are proposed based on ART configuration, and the possibility of its superior characteristics are estimated. The electronic structures of candidate molecules for MOSES devices are also evaluated by simulation. Finally, ART and MOSES devices are evaluated on the basis of the characteristics necessary for information processing integrated circuit devices, and are found to be the most promising candidates for future information processing devices. It also describes several key technologies for the fabrication of these atom/ molecule switching devices.

## 2. Characteristics necessary for information processing devices

Generally, integrated circuit devices should fulfill the following requirements for high performance information processing [4]. They are (a) Input and output (I/O) signal balance, (b) I/O signal isolation, (c) high switching speed, (d) dense integration capability and (e) fabricability. Other factors, such as operation margin, noise immunity, power dissipation and reliability have to be taken into consideration in the integrated circuit design. Among the above five factors, (c) high switching speed has usually been the only criterion for evaluating "new" devices, however it is essential to fulfill the five conditions in a balanced manner. The reason why MOS transistors have been used in integrated circuits so far and are expected to be used down to their limit of around 0.1 µm, is that they meet the above five requirements almost ideally. Therefore superseding devices should satisfy the above five conditions and far excel in (c) high switching speed and (d) dense integration capability compared with those of MOS transistors. These requirements will be the basis of any future information processing devices, even if computer architecture is changed. For example, massively parallel computers will operate faster if the individual processor operates faster.

## 3. Atom/molecule switching devicesprospect for the future

### 3.1. Atom Relay Transistor (ART)

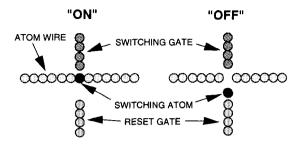

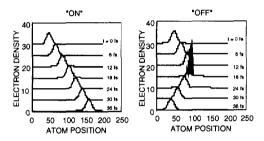

The basic concept of ART is schematically depicted in Fig. 2, in which an individual atom is represented by a circle. ART consists of an atom wire, a switching atom, a switching gate and a reset gate. The atom wire is conductive (ON) when the switching atom is in the atom wire, and it is nonconductive (OFF) when the switching atom is out of the atom wire. The on/off characteristics are simulated by the tight binding method and the results are depicted in Fig. 3, in which 200 atoms are arranged in a straight line with a separation of 0.2 nm. One electron is injected from the left side of the atom wire with an electric field of 3 x 10<sup>5</sup> V/cm, and the electron density flowing in the atom wire is shown with a time interval of 6 fs. The results clearly indicate that ART exhibits on/off switching characteristics according to the position of The movement of the the switching atom. switching atom is made possible by the electric field supplied from the switching gate, as indicated by the

Fig.2 Schematic figure of Atom Relay Transistor (ART), consisting of atom wire, switching atom, switching gate and reset gate

accumulation of high electron density at the switching atom of the atom wire in Fig. 3, which corresponds to an electric field of about 100 mV. Therefore the criterion for the atoms constituting ART is that the switching atoms should be moved by an electric field of less than about 100 mV, while the atoms constituting the atom wire should not be moved. Thus the first requirement, (a) I/O balance for ART is fulfilled if the binding energy of the switching atom E1 and that of atom wire E2 are chosen as E1<100meV<E2. The second requirement, (b) I/O signal isolation, is also met, because ART is a three terminal device. The major advantage of having the reset gate is that synchronous operation of the whole circuit is made possible by applying a reset pulse to put the switching atom back to the original position, just like the clock pulse in present computers.

The switching frequency of ART, which corresponds to the switching speed of the switching atom from the "on" site to the "off" site, should be of the order of several tens of THz, because the intrinsic vibration frequency of an atom is around 100 THz [7]. Recently, the switching speed was reported as 30 THz by a simulation based on the first principle method [8]. These results suggest the potential performances of ART, and the third condition, (c) very high switching speed, is fulfilled.

The basic configuration of ART shown in Fig. 2 suggests that ART can constitute a static memory cell by itself. In addition, ART can formulate dynamic memory cell [4], which uses only about 10<sup>3</sup> times the atom area. Basic logic circuits such as NAND and NOR gates can also be constituted [4]. Rule of thumb estimation of the area occupied by a 10<sup>7</sup> gate logic circuit and a 10<sup>9</sup> bit memory, which corresponds to almost the same integration as

the state-of-the-art supercomputers, suggests around areas 20  $\mu m$  square and 200  $\mu m$  square respectively. Therefore the total area occupied by the ART supercomputer would be about 200  $\mu m$  square, and even the longest signal delay on the chip would be well below the order of  $10^{-12}$  s, which is short enough even for operation at  $10^{12}$  Hz (1 THz). The fourth condition, (d) dense integration, would be fulfilled because device dimensions would be around three orders of magnitude smaller than the ultimate scaled MOS transistors.

Fig.3 Simulation results of the switching characteristics of ART, showing the electron density travelling through the atom wire

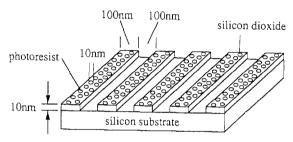

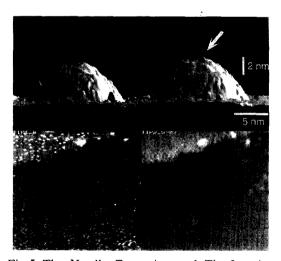

In order to realize ART, it is necessary to manipulate individual atoms by scanning tunneling microscope (STM), an example of which is indicated in the literature [9]. However, ART has to be fabricated on an insulator substrate, which cannot be achieved by the conventional STM. The atomic force microscope (AFM) [10] was invented to overcome this problem, however, the resolution is not high enough to manipulate individual atoms. Beam assisted STM (BASTM) [11] is the most promising solution to this problem, because of its capability for observing insulators as shown in Fig. 4. The operation principle is based on the activation of carriers in the insulator by an irradiating beam, such as electron, ion and photon beams.

In order to manipulate individual atoms by STM, it is necessary to use tips with a very controlled apex. The Needle Formation and Tip Imaging (NFTI) method [12] delineates the three-dimensional tip apex image and in-situ evaluation of the apex is made possible. An example is shown in Fig. 5, where a tip with a very sharp, probably single atom apex provides a clear atomic resolution image, while a dull tip offers a very noisy, unclear image of the same Si (111) 7x7 clean surface. The

principles of the NFTI method are as follows: (1) prepare clean reconstructed silicon surface, (2) apply more than 6 volts to the tip and form a nano-needle structure and (3) delineate the tip image using the nano-needle structure. Reproducibility of NFTI method was demonstrated by writing Kanji Characters on clean Si surface and an example is shown in Fig. 6. These Kanji Characters read, Hi-Tachi-Sei-Saku-Sho, which stands for Hitachi, Limited, each measuring a 50 nm square of area. Each character is made up of nano-needle structures placed in the 16 x 16 dot matrix, and these five ideographs were written by choosing the appropriate sites form the 16 x 16 dots and applying negative voltages to the tip.

Still, the time required to align the atoms necessary to fabricate a supercomputer with a 10<sup>7</sup> logic gate and a 10<sup>9</sup> bit memory would be too long,

Fig.4 Beam Assisted Scanning Tunneling Microscope (BASTM) observation of a 100 nm line and space patterns formed in a 10 nm thick silicon dioxide layer, thermally grown on silicon substrate with 10 nm diameter resist dots: schematic figure (top) and BASTM micrograph (bottom)

since the number of atoms in these devices is of the order of 1010. Therefore some unconventional method, such as self-organization, needs to be adopted. An example of a solution is described in reference [13], in which a single cesium (Cs) atom row aligns itself to form atom wire on a gallium arsenide (GaAs) surface. Though this structure might not be a straight-forward solution due to conductance problems, the self-assembly method of forming atom wire structures should make it possible to fabricate ART based circuits in a reasonably short time. Therefore the fifth requirement, (e) fabricability would be met using BASTM [11], NFTI [12] and the self-assembly phenomenon of the atoms on substrates.

## 3.2. Molecular Single Electron Switching (MOSES) Device

Molecular devices attracted attentions when they were proposed in 1980 by Carter [14], but the interest gradually faded away due to several causes such as inaccessibility to individual molecules and the slow switching speed of molecules for an information processing device. However, with the development of STM technology, it has become possible to manipulate and to access individual

Fig.5 The Needle Formation and Tip Imaging (NFTI) method, demonstrating the effect of the tip apex structure on the quality of STM image; atom scale protrusion indicated by an arrow (top right) is essential for the atomic resolution image of Si (111) 7x7 structure (bottom right)

Fig.6 Kanji characters written by the NFTI method, which read Hi-Tachi-Sei-Saku-Sho (Hitachi, Ltd.). Each character is made up of a 16x16 dot nano needle structures.

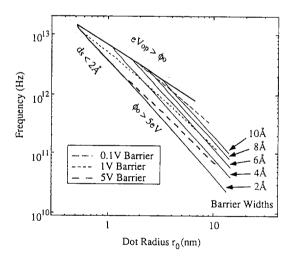

molecules by STM. In addition, recent progress in single electron tunneling (SET) devices [15] is attracting attention because of their potentially superior operation characteristics. The ultimate operation speed of SET devices was simulated and typical results are shown in Fig. 7 [16]. These results indicate that a quantum dot size of less than 1 nm is necessary to obtain a really high performance SET device, and that the tunnel barrier width must

Fig. 7 Simulation results of the ultimate operation speed of SET device [16]: less than a 1 nm dot radius is essential for the high performance operation

also be very thin, less than 1 nm. Conventional fabrication technology can achieve neither the resolution nor accuracy at this dimension. A molecular system should enable superior dimensional control, because the dimension is determined by the number of bonds within the molecule. Therefore the molecule is probably the most appropriate system for realizing high performance SET devices.

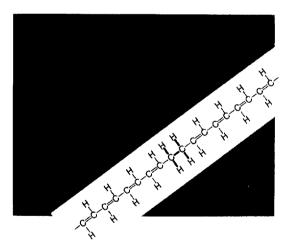

MOSES devices, consisting of conducting polymer and insulating polymer, are schematically shown in Fig. 8 together with the electron density calculated by a molecular orbital (MO) method [5]. In the figure, polyacetylene and polyethylene molecules were chosen as conducting and insulating molecules respectively. The insulator part acts as a tunnel barrier, and the conducting polymer island as a quantum dot, thus SET structure can be constructed. Three terminal devices should also be realizable by synthesizing appropriate molecular structures. The ultimate speed of a MOSES device should be of the order of 10 THz if the quantum dot size is reduced to about 0.3 nm (single atom), as indicated in Fig. 7.

Fig.8 Schematic figure and electron density simulation of possible Molecular Single Electron Switching (MOSES) device, consisting of conducting polymer (ex. polyacetylene) and insulating polymer (ex. polyethylene): electron density distribution suggests conductor part and insulator part in the molecule, and three terminal device should be made possible

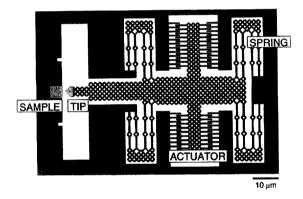

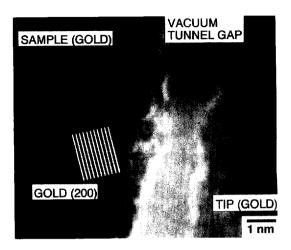

It would not be so difficult to synthesize conducting/insulating molecules with particular structures, such as gates and branches, and the major technological challenge would be the access to individual molecules. Recently, a novel micromachine scanning tunneling microscope (µ-STM) was proposed for molecule manipulation [17]. The drawing of the total u-STM design is shown in Fig. 9. Using the u-STM, the vacuum tunneling gap between the tip apex and sample was successfully observed by transmission electron microscope (TEM), as shown in Fig. 10. The two electrodes are made of gold, and thiol groups on both ends of the conducting molecule would easily make contacts to the electrodes [18]. Therefore the electrical conduction characteristics of the molecule should be reliably measurable, and the high performance of MOSES devices should be demonstrable.

Fig.9 Micromachine STM design for molecule manipulation: Two and Three dimensional devices were also fabricated and found to work.

### 4. Evaluation of candidate devices

The candidate switching devices for the next decade, including quantum devices, conventional single electron devices, conventional molecular devices, ART and MOSES devices, were evaluated according to the five indispensable factors listed above, and the results are summarized in Table 2. As shown in the table, MOS transistors almost ideally fulfill all the requirements, while the quantum devices cannot necessarily be integrated

Fig.10 Transmission electron microscope (TEM) picture of a vacuum tunneling gap between micromachine STM tip apex and sample: This technology would enable to manipulate single molecule.

more densely or fabricated more easily than the MOS devices. Sometimes they may not necessarily fulfill even the I/O signal balance requirements. Conventional molecular devices, on the other hand, demonstrate very high integration density, while the switching speed is extremely slow if the switching principle is based on a structural transformation [14]. Single electron devices may not be so densely integratable, because of the difficulty of fabricating small structures using conventional integrated circuit technology, since the fabrication as well as size control of structures measuring less than 10 nm would probably become almost impossible by conventional fabrication technology [19].

The integration density and switching speed of ART and MOSES devices should be two to three orders of magnitude higher than those of MOS devices [8,16]. Therefore ART and MOSES devices are the most promising candidates for future information processing integrated circuit devices. However, as explained before, fabrication technology has not yet reached the stage where the device performances can be demonstrated. Highly concentrated endeavor in the field of atom/molecule manipulation technology is required before these devices can be realized. In addition, the switching energies of these devices have to be examined in order to avoid thermal and quantum fluctuations [4].

Other problems, such as reliability of operation, heat dissipation and noise immunity have to be taken into consideration in the integrated circuit design.

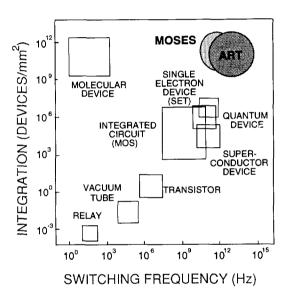

The candidate nano scale devices listed in Table 2, in addition to the historical information processing electron devices listed in Table 1, were evaluated semi-quantitatively in terms of speed and integration capability, which are two of the most important factors among the above five factors. The intrinsic speed (the maximum possible operation frequency) and integration (the maximum device number per unit area) of these devices are estimated, and plotted in Fig. 11. Human beings started information processing using mechanical relay. The very slow and unreliable operation of mechanical relay (mechanical electronics) was soon replaced by a vacuum tube [20] (vacuum electronics). Then the invention of transistors [21] revolutionized the computer, and solid state electronics devices including integrated circuits [22] dominated information processing. As indicated in Fig. 11, the innovation, or paradigm shift (e.g. from mechanical electronics to vacuum electronics to solid state electronics), has been accomplished because the performances of the latter devices are superior to those of preceding ones by an order of magnitude of at least two.

Now that solid state electronics devices are approaching their limits, candidate devices are expected to supersede them. Conventional molecular devices exhibit very high integration density, however, their operating speed is extremely slow and they cannot be prime candidates for future devices. Quantum devices demonstrate better characteristics in terms of integration and switching speed, however, they are not necessarily more densely integratable

Table 2 Evaluation summary of the device characteristics based on the requirements necessary for future integrated circuit devices

|                    | MOS     | QUANTUM<br>DEVICE | SUPER<br>CONDUCTOR<br>DEVICE | SET     | MOLECULAR<br>DEVICE | ART | MOSES |

|--------------------|---------|-------------------|------------------------------|---------|---------------------|-----|-------|

| I/O<br>BALANCE     | 0       | Δ                 | $\circ$                      | $\circ$ |                     | 0   | 0     |

| I/O<br>ISOLATION   | $\circ$ | 0                 | Δ                            | $\circ$ | Δ                   | 0   | 0     |

| SPEED              | $\circ$ | 0                 | 0                            | 0       | Δ                   | 0   | 0     |

| INTEG-<br>RATION   | 0       | 0                 | 0                            | 0       | 0                   | 0   | 0     |

| FABRI-<br>CABILITY | 0       | Δ                 | Δ                            | Δ       | Δ                   | Δ   | Δ     |

nor much faster operable than the present silicon MOS transistors. Single electron devices would have to be scaled down to less than 1 nm in order to obtain very high performances. Therefore ART and MOSES devices are likely to be the most promising candidate devices for future information processing integrated circuits, because of their potentially very fast operation speed and dense integration characteristics. Thus paradigm shift from semiconductor electronics to Atom Electronics might take place before 2010, when the present MOS devices collide into their limitations.

Fig.11 Speed-integration evaluation of devices for information processing, comparison of historical and candidate devices with ART and MOSES devices: paradigm shift needs at least two orders of magnitude performance improvements over the preceding device and Atom Electronics might replace semiconductor electronics

#### 5. Conclusions

This paper proposed nano scale switching devices, Atom Relay Transistors (ART) and Molecular Single Electron (MOSES) devices, for the next score, with dimensions of only a few nm, and an operation speed of more than ten Tera Hz. The switching characteristics of ART were demonstrated

by simulation. Fundamental logic circuits such as NAND and NOR gate constitutions were proposed based on ART characteristics, in addition to memory circuits. These logic and memory circuits can integrate a supercomputer in an area 200 µm square, with 10<sup>7</sup> gates of logic circuit and 10<sup>9</sup> bits of memory, and operate at more than Tera (10<sup>12</sup>) Hz. MOSES device structures were also demonstrated by simulation and very dense and fast operation characteristics were foreseen. New technologies indispensable for the fabrication of these nano scale devices were demonstrated, including BASTM, NFTI and µ-STM. Various candidate nano scale devices were evaluated on the basis of the characteristics necessary for future integrated circuit devices, and ART and MOSES devices were found to be the most promising devices for future information processing integrated circuits. Thus, Atom Electronics would be a very probable candidate to supersede the present semiconductor electronics.

### **ACKNOWLEDGEMENTS**

The author would like to express his sincere gratitude to Dr. Shojiro Asai for his support and continuous encouragement throughout the work. He would also like to express his thanks to Dr. Tsuyoshi Uda, Dr. Munehisa Mitsuya, Dr. Tomihiro Hashizume, Mr. Yasushi Tomioka, Dr. Satoshi Watanabe, Dr. Mark I. Lutwyche, Dr. Takashi Goda, Mr. Seiichi Kondo and Mr. Seiji Heike for their contributions to the work. ULSI Research Department and Electron Device Department of Central Research Laboratory, Hitachi, Ltd. are acknowledged for the fabrication of μ-STM chips.

### REFERENCES

- R. H. Dennard, F. H. Gaensslen, H. Yu, V. L. Rideout, E. Bassous and A. L. LeBlanc, IEEE J. Solid St. Circuits, SC-9 (1974) 256.

- T. Sugano, "VLSI Process Data Handbook", Science Forum, Tokyo, 1990. (in Japanese) R.W.Keyes, Physics Today, 45 (1992) 42.

- "Mesoscopic Phenomena in Solids", B. L. Al'tshuler, P. A. Lee and R. A. Webb (Eds.), Northholland, Amsterdam, 1991.

M. A. Reed, Scientific American, 266 (1993)

- Y. Wada, T. Uda, M.I.Lutwyche, S. Kondo and S.Heike, J. Appl. Phys., 74 (1993) 7321.

- 5. Y. Wada, Trans. IEICEJ, OME 93-54 (1994) 31. (in Japanese)

- "Parallel Computers 2", R. W. Hockney and C. R. Jesshope, Adam Hilger, Philadelphia, 1988.

- 7. "Diffusion in Solids", P.G.Shewmon, McGraw Hill, New York, 1963.

- 8. P.von Allmen and K.Hess, Phys. Rev., to be published

- D. M. Eigler and E. K. Schweizer, Nature, 344 (1990) 524.

- G.Binnig, C.F.Quate and C.Gerber, Phys. Rev. Lett., 56 (1986) 930.

- S. Heike, Y. Wada, S. Kondo, M. I. Lutwyche, K. Murayama and T. Kuroda, Appl. Phys. Lett., 64 (1994) 1100.

- S. Heike, T. Hashizume and Y. Wada, Extended Abstracts Intnl. Conf. Solid St. Devices and Mater., Osaka, 1995.

- 13. L.J.Whitman, J.A.Stroscio, R.A.Dragoset and R.J.Celotta, Science, 251 (1991) 1206.

- 14. "Molecular Electronics", F. T. Hong (Ed.) Plenum Press, New York, 1989.

- K. K. Likharev, IBM J. Res. Devolop., 32 (1988) 144.

- M. I. Lutwyche and Y. Wada, J. Appl. Phys., 75 (1994) 3654.

- 17. M. I. Lutwyche and Y. Wada, Appl. Phys. Lett., 66 (1995) 2807.

- 18. G. M. Whitesides and P.E. Laibinis, Langmuir, 6 (1990) 87.

- 19. T. Yoshimura, H. Shiraishi, J. Yamamoto and S. Okazaki, Appl. Phys. Lett., 63 (1993) 764.

- 20. "Vacuum Tubes", K. R. Spangenberg, McGraw-Hill, New York, 1948.

- "Transistor Technology", H. E. Bridgers, J. H. Scaff and J. N. Shive (Eds.), D. Van Nostrad, Prinston, 1958.

- 22. J. Kilby, IEEE Trans. Electron Devices, ED-23 (1976) 648.